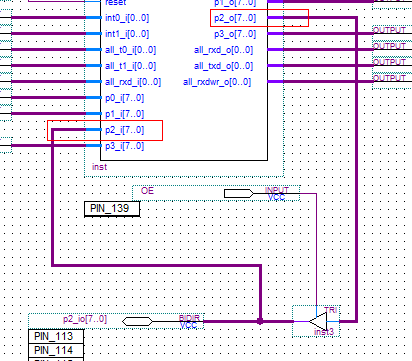

mc8051 IP 中如何用px_i口和px_o口组成px_io双向口

时间:10-02

整理:3721RD

点击:

图中的p2_o和p2_i组成p2_io,输出丁点没问题,只是读时,读回的值好像是p2_o输出的值!?

单片机程序是:

- OE = 1;

- SD = reg;

- AEN = 0;

- CMD = 0;

- IOR = 1;

- IOW = 0;

-

- AEN = 1;

- IOW = 1;

- printf("read reg op you write: %02bx\r", SD);

-

- /* read data from reg */

- AEN = 0;

- CMD = 1;

- IOR = 0;

- IOW = 1;

- OE = 0;

- udata = SD;

-

- AEN = 1;

- IOR = 1;

- printf("read reg op you read: %02bx\r", udata);

- // putchar(udata);

- return udata;

- }

两次输出的都是一个值...

那位大神给瞅瞅啊!感激涕零啊

这个是驱动能力问题。

那个TRI当OEN无效时,确定输出是z吗?也就是低驱动能力输出?

不知道你的这个部分是怎么实现的?是在PCB上用了个芯片?还是在FPGA或者Asic里实现的?

mc8051 是标准 8051,功能很烂,看看就好,没有学习的必要..

感谢您的关注!是在FPGA里实现的,直接用的tri;这种使法对么?

感谢您的关注!只是问题就在这放着,不是不太好么?

FPGA部分的代码怎么写的?

您好!这部分就是用原理图搭的,生成的代码是:

- module mc8051_test(

- clock,

- reset,

- int0_i,

- int1_i,

- t0_i,

- t1_i,

- OE,

- rxd_i,

- p0_i,

- p1_i,

- p3_i,

- rxdwr_o,

- rxd_o,

- txd_o,

- p0_o,

- p1_o,

- p2_io,

- p3_o

- );

- input clock;

- input reset;

- input int0_i;

- input int1_i;

- input t0_i;

- input t1_i;

- input OE;

- input rxd_i;

- input [7:0] p0_i;

- input [7:0] p1_i;

- input [7:0] p3_i;

- output rxdwr_o;

- output rxd_o;

- output txd_o;

- output [7:0] p0_o;

- output [7:0] p1_o;

- inout [7:0] p2_io;

- output [7:0] p3_o;

- wire SYNTHESIZED_WIRE_0;

- wire SYNTHESIZED_WIRE_1;

- wire [7:0] SYNTHESIZED_WIRE_2;

- mc8051_top b2v_inst(

- .clk(SYNTHESIZED_WIRE_0),

- .reset(SYNTHESIZED_WIRE_1),

- .all_rxd_i(rxd_i),

- .all_t0_i(t0_i),

- .all_t1_i(t1_i),

- .int0_i(int0_i),

- .int1_i(int1_i),

- .p0_i(p0_i),

- .p1_i(p1_i),

- .p2_i(p2_io),

- .p3_i(p3_i),

- .all_rxd_o(rxd_o),

- .all_rxdwr_o(rxdwr_o),

- .all_txd_o(txd_o),

- .p0_o(p0_o),

- .p1_o(p1_o),

- .p2_o(SYNTHESIZED_WIRE_2),

- .p3_o(p3_o));

- assign SYNTHESIZED_WIRE_1 = ~reset;

- assign p2_io[7] = OE ? SYNTHESIZED_WIRE_2[7] : 1'bz;

- assign p2_io[6] = OE ? SYNTHESIZED_WIRE_2[6] : 1'bz;

- assign p2_io[5] = OE ? SYNTHESIZED_WIRE_2[5] : 1'bz;

- assign p2_io[4] = OE ? SYNTHESIZED_WIRE_2[4] : 1'bz;

- assign p2_io[3] = OE ? SYNTHESIZED_WIRE_2[3] : 1'bz;

- assign p2_io[2] = OE ? SYNTHESIZED_WIRE_2[2] : 1'bz;

- assign p2_io[1] = OE ? SYNTHESIZED_WIRE_2[1] : 1'bz;

- assign p2_io[0] = OE ? SYNTHESIZED_WIRE_2[0] : 1'bz;

- pll b2v_inst4(

- .inclk0(clock),

- .c0(SYNTHESIZED_WIRE_0));

- endmodule

或者,我应该怎样才能将只能输入(p2_i)和只能输出口(p2_o)组装成可输入、可输出口(p2_io)呢?

从代码来看没有发现问题,你确认当作为输入的时候,OE信号为低电平吗?

假如你提供的代码是真实的,那么当OE=0的时候,P2_io应该就是从外部输入的信号。

OE=1的时候,P2_io应该就是SYNTHESIZED_WIRE_2的信号。

需要注意,当OE=1的时候,外部不能有信号输入,否则可能会把cell打坏的。

会不会cell已经坏了?

努力学习中~谢谢!