Verilog例化pin位宽不同的处理

时间:10-02

整理:3721RD

点击:

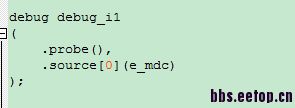

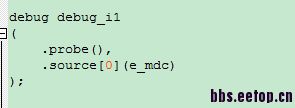

一个模块的source是[7:0]的输出口。如果我只用一个,按下图方式描述:

这样是出错的。但是在VHDL中是允许输出口的某一位映射到改层的某个signal的,但是Verilog怎么描述?

这样是出错的。但是在VHDL中是允许输出口的某一位映射到改层的某个signal的,但是Verilog怎么描述?

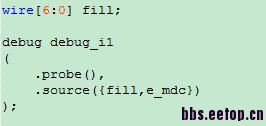

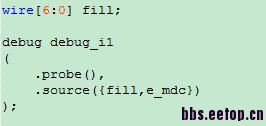

声明一个7bit的wire无用变量做填充是可以实现顶层变量e_mdc与source[0]的映射关系。但是我不想声明这个填充变量,怎么描述呢?

这样是出错的。但是在VHDL中是允许输出口的某一位映射到改层的某个signal的,但是Verilog怎么描述?

这样是出错的。但是在VHDL中是允许输出口的某一位映射到改层的某个signal的,但是Verilog怎么描述?

声明一个7bit的wire无用变量做填充是可以实现顶层变量e_mdc与source[0]的映射关系。但是我不想声明这个填充变量,怎么描述呢?

wire emdc

.source(emdc)

二楼正解,综合工具会把emdc综合到source[0]上,然后报几个warning

emac前面加几个零不就行了

不同位宽的变量传递,最好手动匹配,将不用的位补0或1,否则工具报warning甚至容易导致设计出错。