请教 Xilinx FPGA 如何输出高质量的时钟

时间:10-02

整理:3721RD

点击:

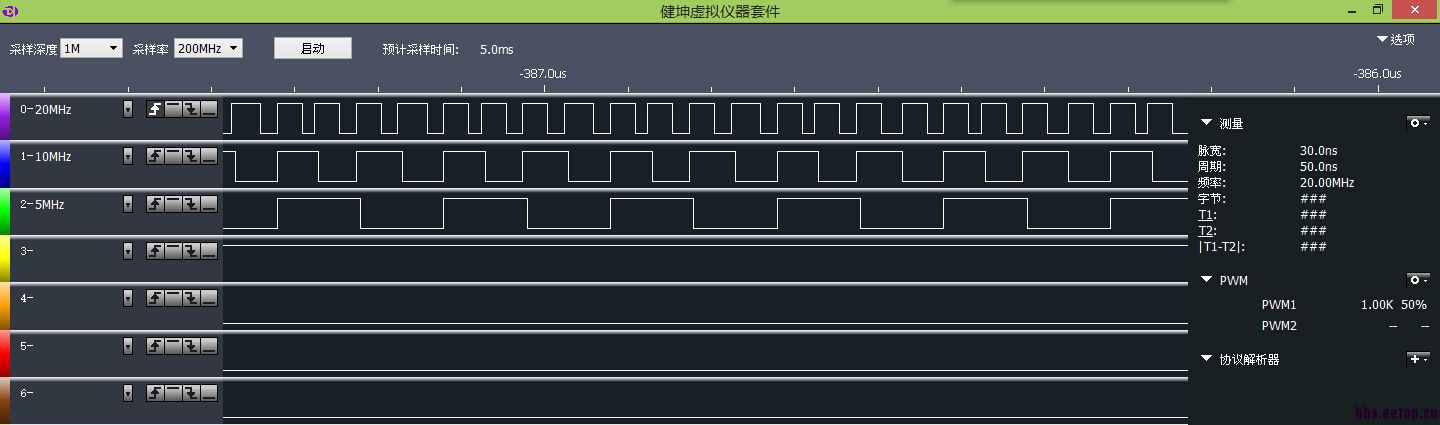

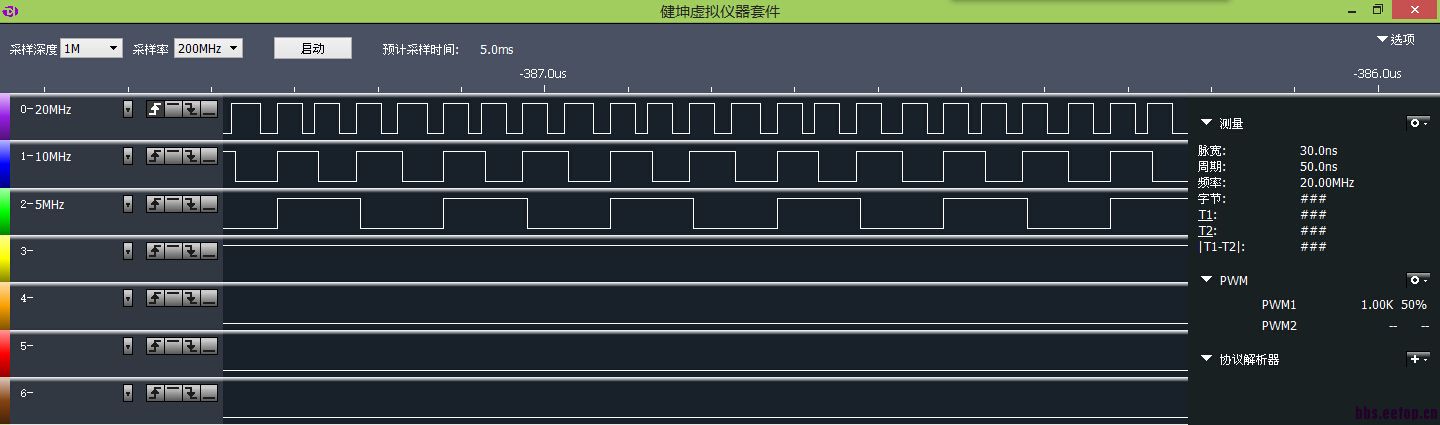

输入时钟 24MHz 通过 PLL 输出 20MHz,10MHz,5MHz 的时钟,用逻辑分析仪测试,发现 20MHz 的时钟输出占空比和频率不稳定,怎么才能输出高质量的时钟?

程序如下:

module CLOCK_PLL_TEST(

input clk,

input rst_n,

output clk_20M,

output clk_10M,

output clk_5M

);

//wire RESET = ~rst_n;

myClockPLL myClockPLL1

(

// Clock in ports

.CLK_IN1(clk), // IN

// Clock out ports

.CLK_OUT20M(CLK_OUT20M), // OUT

.CLK_OUT10M(CLK_OUT10M), // OUT

.CLK_OUT10M(CLK_OUT5M) // OUT

); // OUT

ODDR2

#(

.DDR_ALIGNMENT ("NONE"),

.INIT (1'b0),

.SRTYPE ("SYNC")

)

u1_ODDR2

(

.C0 (CLK_OUT20M),

.C1 (~CLK_OUT20M),

.Q (clk_20M),

.CE (1'b1),

.D0 (1'b1),

.D1 (1'b0),

.R (1'b0),

.S (1'b0)

);

ODDR2

#(

.DDR_ALIGNMENT ("NONE"),

.INIT (1'b0),

.SRTYPE ("SYNC")

)

u2_ODDR2

(

.C0 (CLK_OUT10M),

.C1 (~CLK_OUT10M),

.Q (clk_10M),

.CE (1'b1),

.D0 (1'b1),

.D1 (1'b0),

.R (1'b0),

.S (1'b0)

);

ODDR2

#(

.DDR_ALIGNMENT ("NONE"),

.INIT (1'b0),

.SRTYPE ("SYNC")

)

u3_ODDR2

(

.C0 (CLK_OUT5M),

.C1 (~CLK_OUT5M),

.Q (clk_5M),

.CE (1'b1),

.D0 (1'b1),

.D1 (1'b0),

.R (1'b0),

.S (1'b0)

);

endmodule

逻辑分析仪的带宽太低吧

哦,是逻辑分析仪的问题吗,目前只有个200MHz的。上次用它测过altera的FPGA,输出当时是SPI接口的DAC时钟是50MHz,感觉测出来的信号也是可以的,没这么明显的不稳定。

用一个精度高一点的示波器看看吧,逻辑分析仪不适合看占空比,采样率太低了。