关于设计sd卡控制器接口时序的讨论

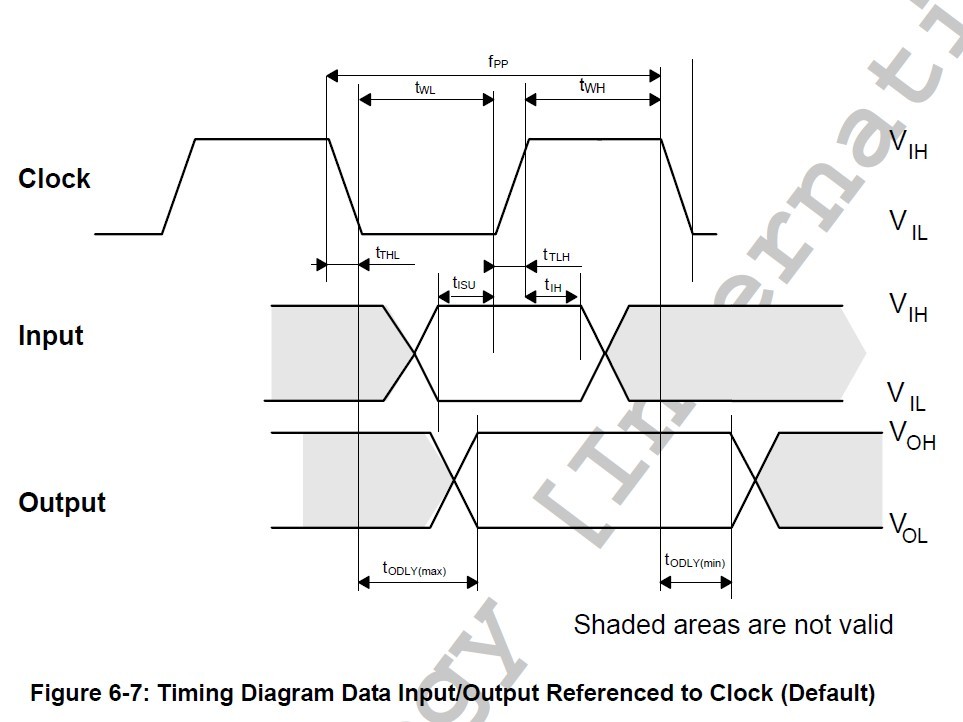

如图,sd卡Bus Timing (Default)如下:

图1

则接口时序我认为可以设计如下(不知能否行的通):

(1)以此时序,sd控制器接口以clk为时钟,则需要在下降沿向sd 卡发数据,上升沿接收sd

如果像这样设计,则sd控制器接口时序逻辑中,时钟上升沿、下降沿都会用到,综合或者后端需要特别考虑时钟

(2)或者,sd控制器接口设计成在发数据,收数据都在上升沿(如下图,上升沿发数据)

图2

如果像这样设计,sd卡控制器逻辑只用时钟的上升沿,那必须要保证图1中的tIH(文档中它的值为5ns) ,才能让sd卡正确收到数据,

即如 图2 , sd卡控制器在时钟上升沿a发数据d0,在时钟上升沿c发d1, 则c到d的数据d1的输出延迟必须保证,才能使sd卡在时钟上升沿c处可靠收到数据d0,则这个输出延迟必须要让综合或者后端去保证。

求大家不吝赐教,积极讨论,不知道我这两个分析是否正确,如果正确,哪个会更好一些呢?

在这里谢谢大家了。

当然SD协议我不大了解, 两者方案都可以的实现,如果你的接口是用在两芯片之间的话, 你都可以用set_output_delay 或者set_input_delay 来约束数据和时钟之间的关系。

设计合适的IO-BUFFER,对调整时序也不错

谢谢, 就是用在芯片之间的(比如一个读卡器),但不知道那种要好一点,或者整体实现简单一点(包括综合,后端等)

都可以,第一种方法时钟下降沿采样之后下一拍你肯定会上升沿打,这个时候的走线延时要小于半个时钟周期是要注意的,第二种方法就是要通过io_delay保持好时钟与数据的关系。

另外还要看你的时钟是随路的还是系统同步的,还有板上的延时

最近做SD卡的接口好像遇到了这个问题,采数据不稳定

我的板子是xilinx的FPGA,如果要做类似于altera的set_output_delay 或者set_input_delay 怎么做,小编知道否?

我现在做的SD卡接口是简单的SPI模式的,时钟是24MHz,上板实调发现,其中两张卡可以成功初始化,但是读写操作不能正确响应,而且SD卡的反应是随机的,而另一张卡连CMD0都无响应。例如:

写操作,有可能写完成而且收到SD卡返回的状态后,SD卡的数据输出端就一直为低,这样FPGA就一直认为SD卡处于忙的状态;

读操作,SD卡收到读命令之后,正确返回0x00h,然后FPGA等待开始令牌0xFEh,但是SD卡的数据输出端一直为高,这样FPGA就一直等待;

从仿真上来看,功能是没有问题的,由于没有SD卡的仿真模型,没法做时序仿真,我现在开始怀疑是不是真的是时钟和数据线延迟的问题。

以我看了几周的dc文档的理解,set_output_delay ,set_input_delay好像不能解决我上面说的那个问题(具体没有做过,不知道),不过可以用楼上说的想办法调整io脚输出的时钟和数据之间的时序,以满足协议上的时序要求。

具体还是要看看xlinx的约束文档吧,这个我也不是很清楚

25M的逻辑 不需要这些

现在也在做SD卡了,我选的是第一种方案,感觉其实SD模式时序,和SPI时序是一样的,-----都是FPGA下降沿设置数据,FGPA上升沿锁存数据;SD卡也是下降沿设置数据,上升沿锁存数据。目前做了CMD6命令,未发现大的BUG,可能后期需要做下约束。

fpga 读取 16G的SD卡第一扇区,数据线一直为高。SD4线模式。CMD17参数为全0.初始化成功,已用ACMD42命令去掉Data3的上拉电阻。在chipscope里看到4位的数据线一直为高,根本就检测不到开始位的‘0’。请问是什么原因啊? 对了,CMD17的响应是0x900.