关于Xilinx PCIe IP核仿真

其他接口比如cfg给的无效或者不赋值。这样我给发送通道发了数据,我想知道pci_exp_txn0,pci_exp_txp0差分对信号是不是有对应的数据出来,结果仿真的时候发现并不如我所愿,输出信号trn_tdst_rdy_n一直是1,是无效的,也就是说trn_td数据实际上没进核里面发送,pci_exp_txn0,pci_exp_txp0差分对信号也没有出来。

其他接口比如cfg给的无效或者不赋值。这样我给发送通道发了数据,我想知道pci_exp_txn0,pci_exp_txp0差分对信号是不是有对应的数据出来,结果仿真的时候发现并不如我所愿,输出信号trn_tdst_rdy_n一直是1,是无效的,也就是说trn_td数据实际上没进核里面发送,pci_exp_txn0,pci_exp_txp0差分对信号也没有出来。所以我就不知道哪里不对了,请问大神们怎么样才能让trn_tdst_rdy_n有效。

这个值得顶一下!一般遇到的问题要从应用手册中找原因!

谢谢,手册上关于这个信号没有详细的说明啊,因为是输出信号,没有说怎么样才能让它有效

应用pcie的话,在建立模块的时候应该会有一个example的工程!你可以参考那个仿真!

谢谢,看来只有回去啃硬骨头了,个个都是上千行代码

是不是我这样的仿真做法是不可取的?

link_up信号看了吗 是否有效

你仿真的时候是将两个pcie设备连在一起仿的吗

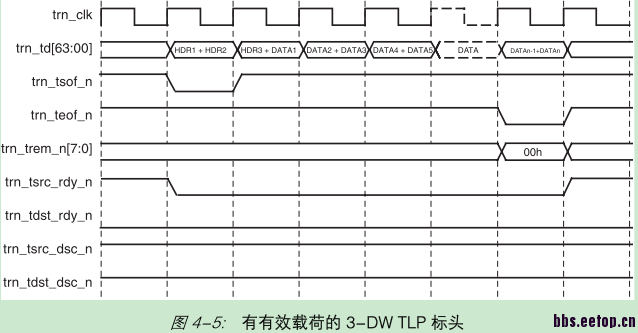

谢谢解答!我不是两个PCIe设备连着仿,我现只加了sys_clk,sys_reset_n两个系统接口信号,和按照上面那张时序图加了trn_tsof_n,trn_teof_n, trn_td[63:0], trn_trem_n[7:0], trn_tsrc_rdy_n这些发送通道的输入信号,我的想法就是先只看看发送通道给数据之后pci_exp_txn0和pci_exp_txp0会不会出连续的数据。你说的link_up波形一直显示是红色的。关于这个信号,ug341是这么说的:事务上行链接:低有效。当核与连接的上行链路合作伙伴端口已就绪并能够交换数据包时,事务上行链接置为有效。当核与链路合作伙伴尝试建立通信时,以及当与链路合作伙伴的通信因传输通道错误而丢失时,事务上行链接置为无效。

似乎我仿的时候核没有让它有效,请问,核怎么样才会让它变为有效呢?

pcie我也没弄过,不过xilinx各个模块都有一个example的例子教你如何使用它的IP,你可以先研究他的例子,然后自己在修改。

个人觉得你这样仿真是不对的,待测设备对端必须连接一个设备,两个设备互联,模拟pcie链路上电进行链路训练的过程,链路训练成功,link_up有效,表示可以进行正常的数据交换;你这对端设备没有,link_up一直无效,ready肯定也一直是高。记住,一切事务的交换都是在link_up有效的前提下进行的。 另外,不用给我翻译link_up的意思,还用红字标识。

你可以看看生成pcie核之后的example,那里边就有一个RP和一个EP,你可以着重看看它是怎么发数据的

非常感谢您的不吝赐教!

学习了。

貌似可以啊

什么可以?

直接看vivado自带的example仿真实例,如果你用的是questasim仿真,可以考虑在vivado工具上设置questasim仿真,然后会在behav文件夹下生成该仿真对应的do文件,看看do文件中调用了哪些文件,是如何执行的,就可以按照这种思路搭建pcie的仿真平台了,这个pcie的仿真我也搞了2天才搞定,确实挺麻烦的。另外,仿真的时候开始是不link up的,需要过大约100us左右吧,才能link上,需要耐心等待

谢谢解答,不过你说的vivado 的example在哪啊?平时比较少用vivado

有一个问题就是怎么样才会让IP核的link_up有效呢,sys_rst_n复位之后一直没有看到它link up?协议上说是要上游链路准备好之后才会link up。

你好,我现在有一个问题就是怎么样才会让IP核的link_up有效呢,我自己写的仿真sys_rst_n复位之后一直没有看到它link up?协议上说是要上游链路准备好之后才会link up,那仿真的时候是怎么模拟链路准备好的呢,IP核又怎么知道这然后link up的呢?

如果你用的是ISE,那么你在生成pcie的ip核之后(不管是在ISE里生成的还是单独用core generator生成的),都会有一个关于pcie核的文件夹,这个文件夹里有个子文件夹叫example,你把这个子文件夹里的源文件都加载到工程里,就会看到一个仿真文件的层次结构图,顶层文件貌似叫board,时间久了忘记了,board下会有两个pcie设备,一个是endpoint(EP),一个是root complex(RC)。至于EP和RC在上电时是怎么通过链路训练建立连接的,仿真文件都已经做好了,如果你想学习链路训练的过程,请参考相关资料。

不要把pcie想的太简单,脑袋一拍上来就搞,先看看人家的example怎么弄的,大致清楚了再说。不要求你看example里的每一个代码,但是你现在连链路训练需要两个设备互联都没搞明白,还怎么玩耍。

2770422249 你还是加我qq吧 老这样太慢太麻烦

在生成ipcore的界面,有个打开 example 的界面

link_up信号看了吗 是否有效

你这样仿真怎么可能出现数据,只是添加参考时钟和复位信号是不能让pcie工作的,对于一个pcie设备,是需要一个主机的或者pcie桥,在pcie设备插入pcie槽时,他要和对端主设备进行链路训练,完全跳转玩两路建立状态,才能完成物理上的建立,这样你才能进行发送数据。利用exemple里的仿真程序经行仿真,就可以了。在example里的仿真程序里有一个pcie根设备,他可以完成主板和pcie设备的过程!

高手啊!以后如果调试pcie的话,加你QQ,不吝赐教啊!

谢谢!之前我也是想当然了,没有深入理解PCIe内容。

这么仿真是不对的,PCIe是端到端设备,之前这么做完全是没理解PCIe的基本性质

同意楼上的,应该有个PCIe的BFM的。