自己写的流水线乘法器问题

时间:10-02

整理:3721RD

点击:

module chengfaqi(

input [3:0] ain,

input [3:0] bin,

input clk, rst_n,

output [7:0] cout

);

reg [3:0] ain_reg;

reg [3:0] bin_reg;

reg [3:0] cout0;

reg [4:0] cout1;

reg [5:0] cout2;

reg [6:0] cout3;

reg [7:0] cout_reg;

always@(posedge clk or negedge rst_n)

if(!rst_n)

begin ain_reg <= #1 4'b0;

bin_reg <= #1 4'b0;

end

else begin ain_reg <= #1 ain;

bin_reg <= #1 bin;

end

always@(posedge clk or negedge rst_n)

if(!rst_n)

begin

cout0 <= #1 4'b0;

cout1 <= #1 5'b0;

cout2 <= #1 6'b0;

cout3 <= #1 7'b0;

cout_reg <= #1 7'b0;

end

else

begin

cout0 <= #1 (bin[0] == 1)?ain:4'b0;

cout1 <= #1 (bin[1] == 1)?{ain,1'b0}:5'b0;

cout2 <= #1 (bin[2] == 1)?{ain,2'b00}:6'b0;

cout3 <= #1 (bin[3] == 1)?{ain,3'b000}:7'b0;

cout_reg <= #1 cout1 + cout2 + cout3 + cout0;

end

assign cout = cout_reg;

endmodule

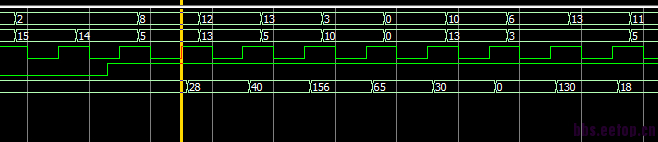

仿真的波形如图:

问题来了,输出的结果怎么只延时一个时钟周期呢?我插入了三个寄存器啊,至少是个周期啊,结果是对的,但是不了解为什么?

input [3:0] ain,

input [3:0] bin,

input clk, rst_n,

output [7:0] cout

);

reg [3:0] ain_reg;

reg [3:0] bin_reg;

reg [3:0] cout0;

reg [4:0] cout1;

reg [5:0] cout2;

reg [6:0] cout3;

reg [7:0] cout_reg;

always@(posedge clk or negedge rst_n)

if(!rst_n)

begin ain_reg <= #1 4'b0;

bin_reg <= #1 4'b0;

end

else begin ain_reg <= #1 ain;

bin_reg <= #1 bin;

end

always@(posedge clk or negedge rst_n)

if(!rst_n)

begin

cout0 <= #1 4'b0;

cout1 <= #1 5'b0;

cout2 <= #1 6'b0;

cout3 <= #1 7'b0;

cout_reg <= #1 7'b0;

end

else

begin

cout0 <= #1 (bin[0] == 1)?ain:4'b0;

cout1 <= #1 (bin[1] == 1)?{ain,1'b0}:5'b0;

cout2 <= #1 (bin[2] == 1)?{ain,2'b00}:6'b0;

cout3 <= #1 (bin[3] == 1)?{ain,3'b000}:7'b0;

cout_reg <= #1 cout1 + cout2 + cout3 + cout0;

end

assign cout = cout_reg;

endmodule

仿真的波形如图:

问题来了,输出的结果怎么只延时一个时钟周期呢?我插入了三个寄存器啊,至少是个周期啊,结果是对的,但是不了解为什么?

哪来的三级寄存器?两级好不好!这里“cout0 <= #1 (bin[0] == 1)?ain:4'b0;”的ain、bin,你是不是想用 ain_reg 、bin_reg的?

对的,昨天晚上睡觉的时候,想到了可能是这个问题,我再去试试

bingo是这个问题,本来是想用ain_reg和bin_reg的,写错了,我擦,检查的时候没有检查出来