verilog小白入门,求助初值设置问题?

时间:10-02

整理:3721RD

点击:

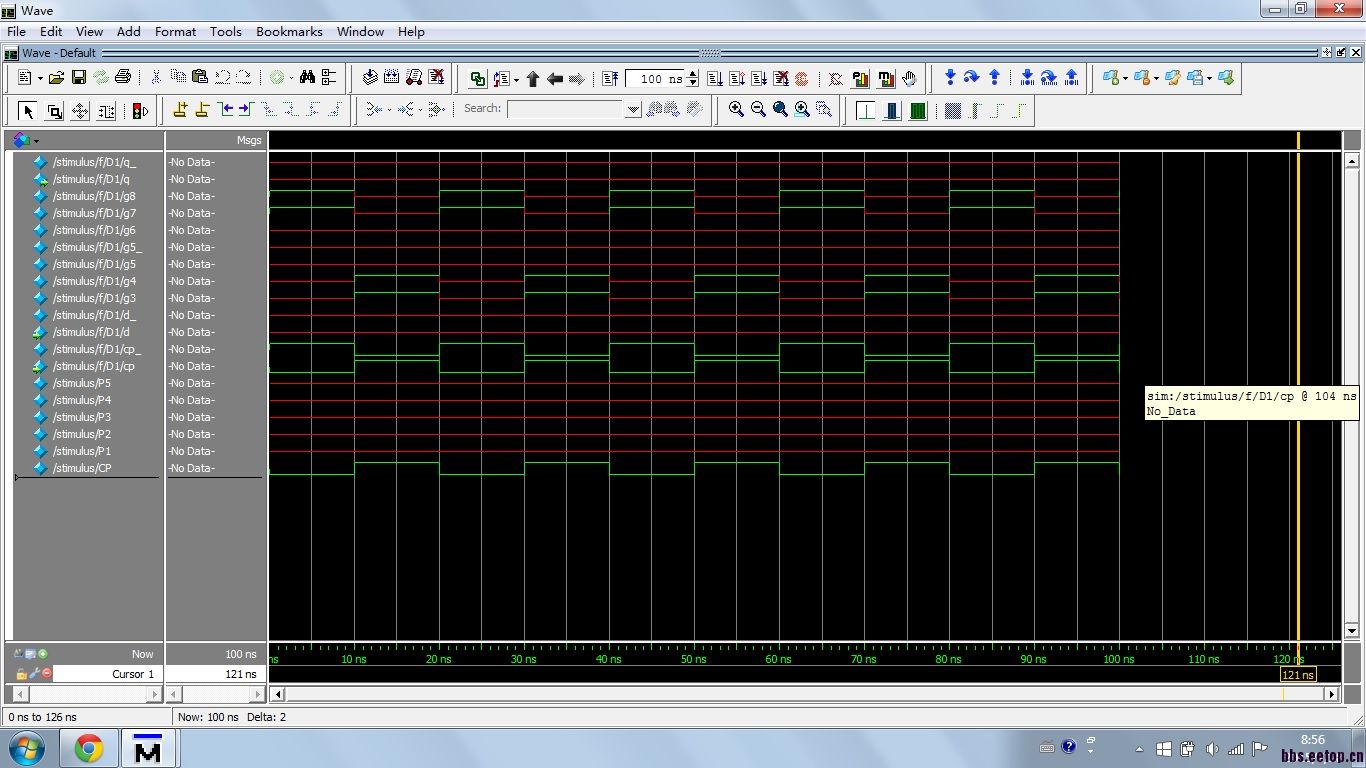

小白一枚,打算熟悉一下门级描述。利用边沿触发器搭建一个摩尔电路。边沿触发器检查过了没有问题,但最终仿真波形中为不定态。应该是相互连接的问题,初值怎么设置都不对。请各位帮忙解答。代码如下:

module Detff(q,cp,d);

input d;

input cp;

output q;

wire d_,cp_,q,q_,g3,g4,g5,g5_,g6,g7,g8;

not(d_,d);

not(cp_,cp);

nand(g8,d_,cp);

nand(g7,d,cp);

nand(g6,g5,g8);

nand(g5,g6,g7);

not(g5_,g5);

nand(g4,cp_,g5_);

nand(g3,cp_,g5);

nand(q_,q,g4);

nand(q,q_,g3);

endmodule

module spg(cp,p1,p2,p3,p4,p5);

input cp;

output p1,p2,p3,p4,p5;

wire s;

Detff D1(p1,cp,s);

Detff D2(p2,cp,p1);

Detff D3(p3,cp,p2);

Detff D4(p4,cp,p3);

Detff D5(p5,cp,p4);

nor(s,p1,p2,p3,p4);

endmodule

module stimulus;

reg CP;

spg f(CP,P1,P2,P3,P4,P5);

initial

CP=1'b0;

always

#10 CP=~CP;

endmodule

module Detff(q,cp,d);

input d;

input cp;

output q;

wire d_,cp_,q,q_,g3,g4,g5,g5_,g6,g7,g8;

not(d_,d);

not(cp_,cp);

nand(g8,d_,cp);

nand(g7,d,cp);

nand(g6,g5,g8);

nand(g5,g6,g7);

not(g5_,g5);

nand(g4,cp_,g5_);

nand(g3,cp_,g5);

nand(q_,q,g4);

nand(q,q_,g3);

endmodule

module spg(cp,p1,p2,p3,p4,p5);

input cp;

output p1,p2,p3,p4,p5;

wire s;

Detff D1(p1,cp,s);

Detff D2(p2,cp,p1);

Detff D3(p3,cp,p2);

Detff D4(p4,cp,p3);

Detff D5(p5,cp,p4);

nor(s,p1,p2,p3,p4);

endmodule

module stimulus;

reg CP;

spg f(CP,P1,P2,P3,P4,P5);

initial

CP=1'b0;

always

#10 CP=~CP;

endmodule

玩门级的都是高手

呃 不是不是 看的palnitkar那本书 这书先讲的门级 所以就随便找个电路试试 结果 貌似是因为数据类型的问题吧 还望赐教啊

p1 p2 p3 p4 p5 为output,又作为Detff的输入,但是没有模块对它们赋值。

谢谢!我听懂问题出在哪里了。但是,我还是不知道,该怎么debug。就是,这种摩尔型的时序电路,本身就没有输入值。变量定义都是wire型的,我怎么在代码中实现呢?

这样的仿真我还没有做过,主要应该是仿真软件的问题,从代码上看好像没有问题。