FPGA+外部PHY+RJ45 的问题

目前的情况是,用网线一端连电脑,一端连板子上的RJ45端口,将PHY配置在百兆的模式下,可以正常接收电脑发出的包;

但是在千兆模式下,用SIGNALTAP看抓到的包,一直有奇怪的信号,如果电脑不发包,也一直有这些奇怪的信号。如果一次发一个包,基本抓不到,猜测是被奇怪信号淹没,只能一直连续发包,才能抓到,且抓到的数据会有许多错误。求问大神们是否知道是什么原因?

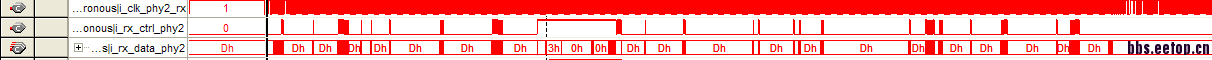

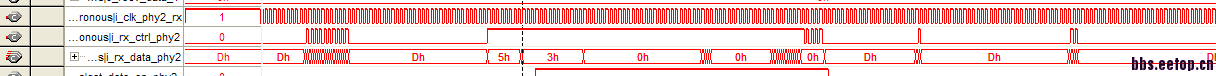

SIGNALTAP抓到的千兆模式下的包如下所示:

小编用哪个型号的PHY?你的连接关系是什么,SFP只能接FPGA的Serdes吧?和PHY怎么连,你的调通了SFP又是什么意思?

88E1512

是的,之前有点问题,后来解决了。

现在是RJ-45有问题了,挺纠结

这个论坛真是不错。

同楼上,SFP和PHY是怎样接的?为何不直接与FPGA的SERDES对接?

SFP的控制信号,包括I2C,都是接FPGA的,就是数据的输入输出经过PHY。

这个没关系,主要是现在RJ45有问题。

求高人帮忙啊!

没人知道吗

低速通高速不通,只能用示波器先分析千兆下物理链路的信号质量了。

千兆时候,signaltap采样时钟设定的是多少呢,以及示波器观察过吗,还有loopback时千兆正常吗

高速能通,但是从信号灯的闪烁来看,即使我没有用发送数据,但是板子还是一直在接收数据,而且速度很快。虽然电脑网卡正常情况下也是会发送一些协议报文,但是速度不会这么快,抓网卡的包,也只有正常报文,没有乱七八糟的报文,用SIGNALTAP来看,就是有很多乱七八糟的数据信号收到。

然后,在百兆的情况下,电脑不发数据,板子只是偶尔接收下电脑发出的其他数据,速度较正常,跟抓包软件抓到的电脑网卡报文速率打不多。然后要是我发送数据,就能正常接收。

用的是FPGA的125M时钟倍频出来的250M时钟。

示波器观察过,但是信号很乱,不知道应该是怎样的,我应该看示波器的什么情况?

LOOPBACK没有尝试过,我准备去尝试一下,主要是看什么的?

你用的示波器采样时钟是多少呀,能采到千兆的数据吗,观察时候,看下时钟沿与数据的对齐情况,

FPGA+外部PHY+RJ45 的问题 不是设计者的问题,是设计方法问题。 对于一个有经验的设计者不会遇到这样的问题。选择一个合适的参考设计是项目启动的关键。 正说,好的开始是成功的一半,走错路了,可能一直都在错误的道路上是……