利用块RAM实现数据延迟的一些问题

时间:10-02

整理:3721RD

点击:

这个是利用块RAM实现a、b两路数据延迟,数据位宽都为32,其中a路延迟16个数据周期,b路延迟8个数据周期,代码如下:

这个程序功能能够实现,仿真结果也正确,但是却出现瑕疵,综合出现结果如下:

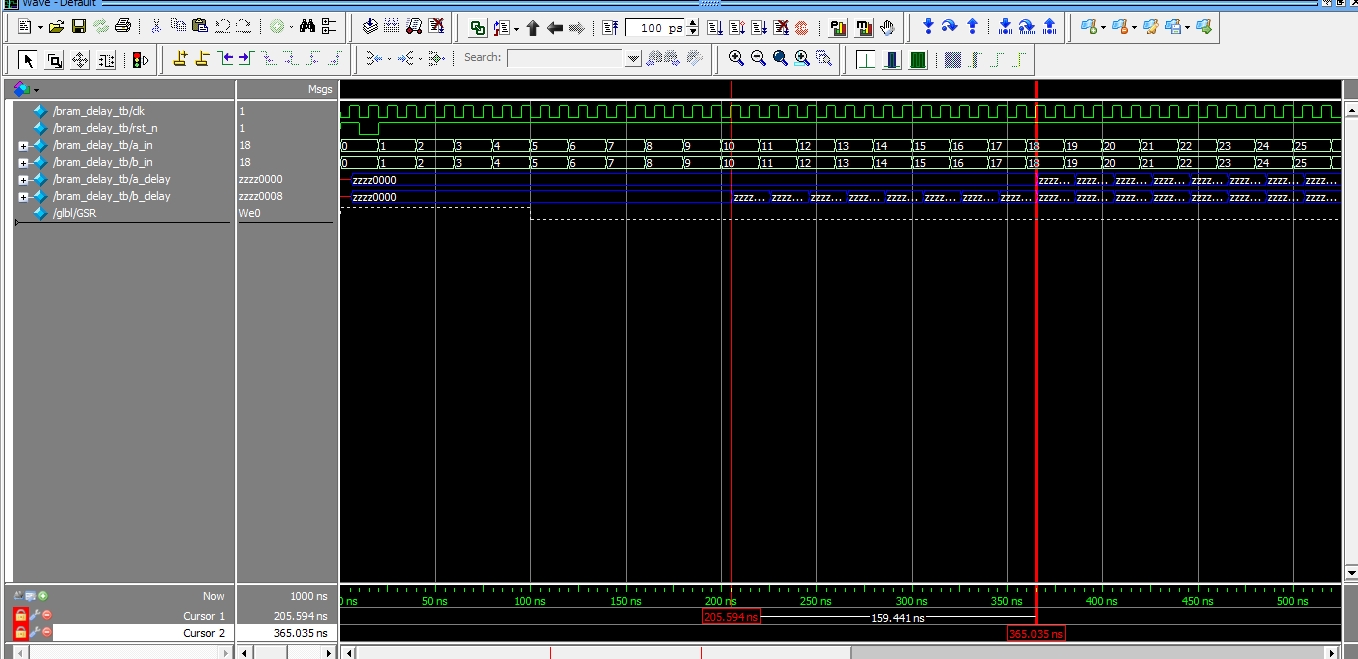

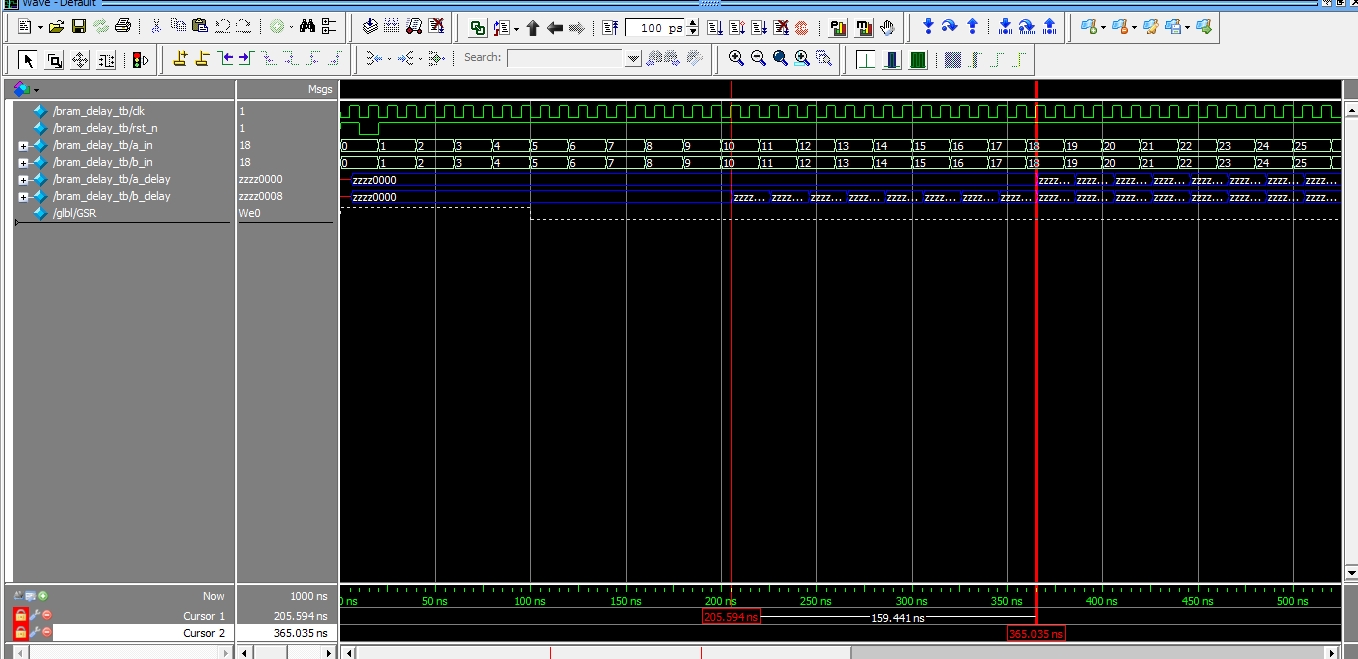

对于a_delay和b_delay都已经初始化了的,为什么还出现这个问题?仿真图如下:

望各位坛友支支招,在此谢谢了!

- `timescale 1ns / 1ps

- //////////////////////////////////////////////////////////////////////////////////

- // Company:

- // Engineer:

- //

- // Create Date: 20:51:45 12/15/2013

- // Design Name:

- // Module Name: bram_delay

- // Project Name:

- // Target Devices:

- // Tool versions:

- // Description:

- //

- // Dependencies:

- //

- // Revision:

- // Revision 0.01 - File Created

- // Additional Comments:

- //

- //////////////////////////////////////////////////////////////////////////////////

- module bram_delay(

- input wire clk,

- input wire rst_n,

- input wire[31:0] a_in,

- input wire[31:0] b_in,

- output reg[31:0] a_delay,

- output reg[31:0] b_delay);

- /*************************************************************************/

- parameter DEL = 1;

- /*************************************************************************/

- wire[5:0] a_addr;

- wire[5:0] b_addr;

- wire[31:0] douta;

- wire[31:0] doutb;

- reg[5:0] a_addr1 = 6'd0;

- reg[5:0] a_addr2 = 6'd0;

- reg[5:0] b_addr1 = 6'd32;

- reg[5:0] b_addr2 = 6'd32;

- reg wea = 1'b0;

- reg web = 1'b0;

- reg flag = 1'b0;

-

- /**************************************************************************/

- always @ ( posedge clk)

- begin

- if( rst_n == 1'b0 )

- begin

- a_delay <= 32'b0;

- b_delay <= 32'b0;

- end

- else begin

- flag <= #DEL !flag;

- if( flag == 1'b1)

- begin

- a_delay <= #DEL a_delay;

- b_delay <= #DEL b_delay;

- wea <= #DEL 1'b1;

- web <= #DEL 1'b1;

- a_addr2 <= #DEL a_addr2;

- b_addr2 <= #DEL b_addr2;

- if( a_addr1 == 6'd31)

- a_addr1 <= #DEL 6'd0;

- else

- a_addr1 <= #DEL a_addr1 + 6'b1;

- if( b_addr1 == 6'd63)

- b_addr1 <= #DEL 6'd0;

- else

- b_addr1 <= #DEL b_addr1 + 6'b1;

- end

- else

- begin

- a_delay <= #DEL douta;

- b_delay <= #DEL doutb;

- wea <= #DEL 1'b0;

- web <= #DEL 1'b0;

- a_addr1 <= #DEL a_addr1;

- b_addr1 <= #DEL b_addr1;

- if( a_addr1 <= 6'd15)

- a_addr2 <= #DEL a_addr1 + 6'd16;

- else

- a_addr2 <= #DEL a_addr1 - 6'd16;

- if( b_addr1 <= 6'd39)

- b_addr2 <= #DEL b_addr1 + 6'd24;

- else

- b_addr2 <= #DEL b_addr1 - 6'd8;

- end

- end

- end

- /*************************************************************************/

- assign a_addr = !flag ? a_addr1 : a_addr2;

- assign b_addr = !flag ? b_addr1 : b_addr2;

- /**************************************************************************/

- bram_16 dut (

- .clka(clk), // input clka

- .wea(wea), // input [0 : 0] wea

- .addra(a_addr), // input [5 : 0] addra

- .dina(a_in), // input [15 : 0] dina

- .douta(douta), // output [15 : 0] douta

- .clkb(clk), // input clkb

- .web(web), // input [0 : 0] web

- .addrb(b_addr), // input [5 : 0] addrb

- .dinb(b_in), // input [15 : 0] dinb

- .doutb(doutb) // output [15 : 0] doutb

- );

- endmodule

这个程序功能能够实现,仿真结果也正确,但是却出现瑕疵,综合出现结果如下:

- WARNING:Xst:916 - "bram_delay.v" line 52: Delay is ignored for synthesis.

- WARNING:Xst:916 - "bram_delay.v" line 55: Delay is ignored for synthesis.

- WARNING:Xst:916 - "bram_delay.v" line 56: Delay is ignored for synthesis.

- WARNING:Xst:916 - "bram_delay.v" line 57: Delay is ignored for synthesis.

- WARNING:Xst:916 - "bram_delay.v" line 58: Delay is ignored for synthesis.

- WARNING:Xst:915 - Message (916) is reported only 5 times for each module.

- WARNING:Xst:2211 - "ipcore_dir/bram_16.v" line 94: Instantiating black box module <bram_16>.

- WARNING:Xst:647 - Input <b_in<31:16>> is never used. This port will be preserved and left unconnected if it belongs to a top-level block or it belongs to a sub-block and the hierarchy of this sub-block is preserved.

- WARNING:Xst:647 - Input <a_in<31:16>> is never used. This port will be preserved and left unconnected if it belongs to a top-level block or it belongs to a sub-block and the hierarchy of this sub-block is preserved.

- WARNING:Xst:1710 - FF/Latch <b_delay_31> (without init value) has a constant value of 0 in block <bram_delay>. This FF/Latch will be trimmed during the optimization process.

- WARNING:Xst:1895 - Due to other FF/Latch trimming, FF/Latch <b_delay_30> (without init value) has a constant value of 0 in block <bram_delay>. This FF/Latch will be trimmed during the optimization process.

- WARNING:Xst:1895 - Due to other FF/Latch trimming, FF/Latch <b_delay_29> (without init value) has a constant value of 0 in block <bram_delay>. This FF/Latch will be trimmed during the optimization process.

- WARNING:Xst:1895 - Due to other FF/Latch trimming, FF/Latch <b_delay_28> (without init value) has a constant value of 0 in block <bram_delay>. This FF/Latch will be trimmed during the optimization process.

- WARNING:Xst:1895 - Due to other FF/Latch trimming, FF/Latch <b_delay_27> (without init value) has a constant value of 0 in block <bram_delay>. This FF/Latch will be trimmed during the optimization process.

- WARNING:Xst:1895 - Due to other FF/Latch trimming, FF/Latch <b_delay_26> (without init value) has a constant value of 0 in block <bram_delay>. This FF/Latch will be trimmed during the optimization process.

- WARNING:Xst:1895 - Due to other FF/Latch trimming, FF/Latch <b_delay_25> (without init value) has a constant value of 0 in block <bram_delay>. This FF/Latch will be trimmed during the optimization process.

- WARNING:Xst:1895 - Due to other FF/Latch trimming, FF/Latch <b_delay_24> (without init value) has a constant value of 0 in block <bram_delay>. This FF/Latch will be trimmed during the optimization process.

- WARNING:Xst:1895 - Due to other FF/Latch trimming, FF/Latch <b_delay_23> (without init value) has a constant value of 0 in block <bram_delay>. This FF/Latch will be trimmed during the optimization process.

- WARNING:Xst:1895 - Due to other FF/Latch trimming, FF/Latch <b_delay_22> (without init value) has a constant value of 0 in block <bram_delay>. This FF/Latch will be trimmed during the optimization process.

- WARNING:Xst:1895 - Due to other FF/Latch trimming, FF/Latch <b_delay_21> (without init value) has a constant value of 0 in block <bram_delay>. This FF/Latch will be trimmed during the optimization process.

- WARNING:Xst:1895 - Due to other FF/Latch trimming, FF/Latch <b_delay_20> (without init value) has a constant value of 0 in block <bram_delay>. This FF/Latch will be trimmed during the optimization process.

- WARNING:Xst:1895 - Due to other FF/Latch trimming, FF/Latch <b_delay_19> (without init value) has a constant value of 0 in block <bram_delay>. This FF/Latch will be trimmed during the optimization process.

- WARNING:Xst:1895 - Due to other FF/Latch trimming, FF/Latch <b_delay_18> (without init value) has a constant value of 0 in block <bram_delay>. This FF/Latch will be trimmed during the optimization process.

- WARNING:Xst:1895 - Due to other FF/Latch trimming, FF/Latch <b_delay_17> (without init value) has a constant value of 0 in block <bram_delay>. This FF/Latch will be trimmed during the optimization process.

- WARNING:Xst:1895 - Due to other FF/Latch trimming, FF/Latch <b_delay_16> (without init value) has a constant value of 0 in block <bram_delay>. This FF/Latch will be trimmed during the optimization process.

- WARNING:Xst:1895 - Due to other FF/Latch trimming, FF/Latch <a_delay_31> (without init value) has a constant value of 0 in block <bram_delay>. This FF/Latch will be trimmed during the optimization process.

- WARNING:Xst:1895 - Due to other FF/Latch trimming, FF/Latch <a_delay_30> (without init value) has a constant value of 0 in block <bram_delay>. This FF/Latch will be trimmed during the optimization process.

- WARNING:Xst:1895 - Due to other FF/Latch trimming, FF/Latch <a_delay_29> (without init value) has a constant value of 0 in block <bram_delay>. This FF/Latch will be trimmed during the optimization process.

- WARNING:Xst:1895 - Due to other FF/Latch trimming, FF/Latch <a_delay_28> (without init value) has a constant value of 0 in block <bram_delay>. This FF/Latch will be trimmed during the optimization process.

- WARNING:Xst:1895 - Due to other FF/Latch trimming, FF/Latch <a_delay_27> (without init value) has a constant value of 0 in block <bram_delay>. This FF/Latch will be trimmed during the optimization process.

- WARNING:Xst:1895 - Due to other FF/Latch trimming, FF/Latch <a_delay_26> (without init value) has a constant value of 0 in block <bram_delay>. This FF/Latch will be trimmed during the optimization process.

- WARNING:Xst:1895 - Due to other FF/Latch trimming, FF/Latch <a_delay_25> (without init value) has a constant value of 0 in block <bram_delay>. This FF/Latch will be trimmed during the optimization process.

- WARNING:Xst:1895 - Due to other FF/Latch trimming, FF/Latch <a_delay_24> (without init value) has a constant value of 0 in block <bram_delay>. This FF/Latch will be trimmed during the optimization process.

- WARNING:Xst:1895 - Due to other FF/Latch trimming, FF/Latch <a_delay_23> (without init value) has a constant value of 0 in block <bram_delay>. This FF/Latch will be trimmed during the optimization process.

- WARNING:Xst:1895 - Due to other FF/Latch trimming, FF/Latch <a_delay_22> (without init value) has a constant value of 0 in block <bram_delay>. This FF/Latch will be trimmed during the optimization process.

- WARNING:Xst:1895 - Due to other FF/Latch trimming, FF/Latch <a_delay_21> (without init value) has a constant value of 0 in block <bram_delay>. This FF/Latch will be trimmed during the optimization process.

- WARNING:Xst:1895 - Due to other FF/Latch trimming, FF/Latch <a_delay_20> (without init value) has a constant value of 0 in block <bram_delay>. This FF/Latch will be trimmed during the optimization process.

- WARNING:Xst:1895 - Due to other FF/Latch trimming, FF/Latch <a_delay_19> (without init value) has a constant value of 0 in block <bram_delay>. This FF/Latch will be trimmed during the optimization process.

- WARNING:Xst:1895 - Due to other FF/Latch trimming, FF/Latch <a_delay_18> (without init value) has a constant value of 0 in block <bram_delay>. This FF/Latch will be trimmed during the optimization process.

- WARNING:Xst:1895 - Due to other FF/Latch trimming, FF/Latch <a_delay_17> (without init value) has a constant value of 0 in block <bram_delay>. This FF/Latch will be trimmed during the optimization process.

- WARNING:Xst:1895 - Due to other FF/Latch trimming, FF/Latch <a_delay_16> (without init value) has a constant value of 0 in block <bram_delay>. This FF/Latch will be trimmed during the optimization process.

- WARNING:Xst:2404 - FFs/Latches <b_delay<31:16>> (without init value) have a constant value of 0 in block <bram_delay>.

- WARNING:Xst:2404 - FFs/Latches <a_delay<31:16>> (without init value) have a constant value of 0 in block <bram_delay>.

对于a_delay和b_delay都已经初始化了的,为什么还出现这个问题?仿真图如下:

望各位坛友支支招,在此谢谢了!

如果只是延时32的话,完全可以用移位寄存器(分布式RAM)实现,用BRAM浪费了

如果考虑到优化的话,确实用分布式RAM比较好,但问题是为什么会出现上述问题?

看这样子是没有复位,小编把rst_n低电平的时间弄长一点。

刚开始在复位时,我是写有延时的,结果还是一样,所以后来我就直接删除了!

数据要先赋值,然后读取啊,你开始仿真,还没有把RAM整个初始化完,那写一段地址的数据进去,读另一段地址的数据出来,那段还没初始化过,自然会是z了。

flag怎么激励的?

按你的写法,flag应是渐段式激励吧?写1后再写0,然后等延迟若干后地址的数据输出。

另外,对a, b路的关系觉得很诡异,按你的想法,a, b路是关系平等的两路数据,只是分别延迟不同地址而已吧?那你用个真双口是为了什么?真双口的数据对A口和B口来说,内容是共享的,那岂不是a, b路数据相互冲突了?

你说的应该没错,应该就是初始化时间不够造成的。我知道真双口RAM的内容是共享的,所以我固定前段地址(0—31)只能写a数据,后段(32—63)数据只能写b数据,而且输出地址也是有设置了的,故我觉得虽然共享,但它们的数据是不会矛盾的,不会有冲突!不知这样是否妥当?

有这样处理自然没问题,不会冲突就好,你还可以直接用两个单口RAM啊,二者在RAM的使用面积上是一致的

是啊,考虑到数据方面,最后还是改成分布式的了,利用器件原语,节省资源。总之,谢谢了!

受教了,谢谢

实现数据延迟最好的方式是用fifo。 你自己用ram外加控制逻辑,如果控制逻辑写的不好很容易出问题。xilinx有源码的fifo好用