关于有源晶振的问题。

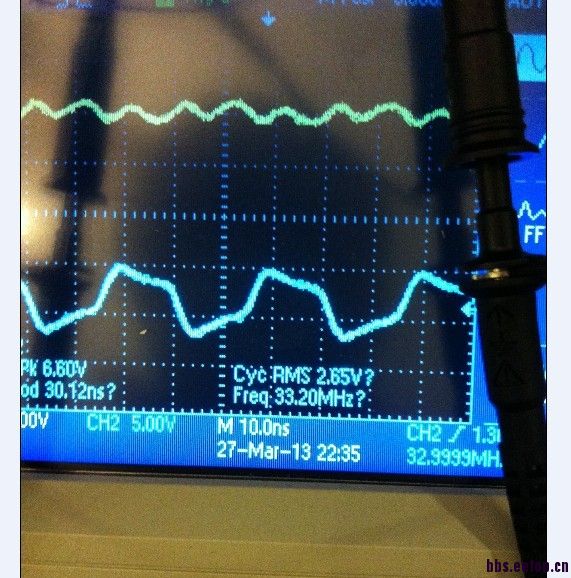

图一

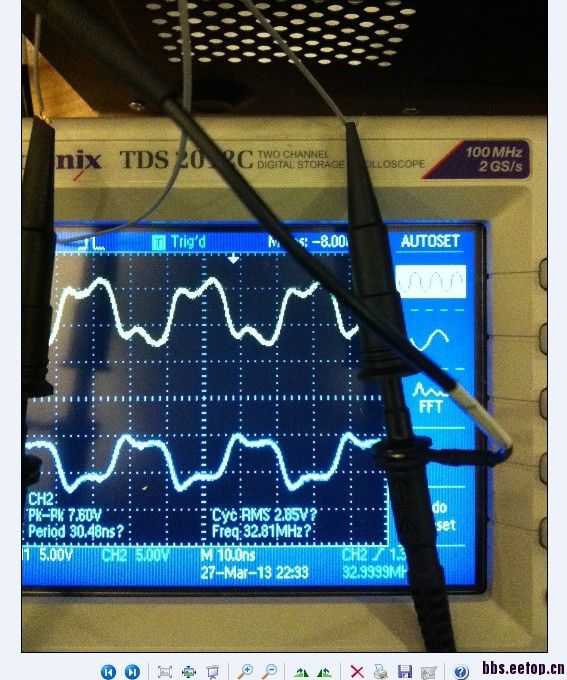

图2

这波形还不错,一看就阻抗不匹配。人家500MHz时钟都能横平竖直的你见过吗。

请问怎么做到的?我是按典型电路接的,vcc与地之间接104的电容,时钟输出接了22欧的电阻。1. 时钟走线从发送端开始到接收端为止,中途不能出现分岔;

2. 时钟走线线宽要恒定;

3. 时钟附近要有恒定地平面(含电源平面),必须能近似成无穷大不间断的平面;

4. (以特征阻抗50欧为例)在接收端并联50欧电阻到地,或到电源,或各100欧到电源和地。或在发送端串联50欧电阻。

5. 除此之外,时钟走线不要有其他任何东西,包括电容什么的。

关于特征阻值的计算,不必知道太细。实用的方法是,满足以上5条后,做PCB时告诉厂商你哪些宽度的线要做成50欧就可以了。

1、分岔指的是什么?过孔吗?时钟线不是就一条吗,怎么会出现分岔?

2、线宽恒定,那粗细有要求吗?请问7mil应该吗?3、铺铜算不算是恒定的地平面?电源平面是什么概念,我就拉了根40mil的电源线连晶振vcc端。

4、发送端和接受端不是连在一起的吗?接收端并联50欧电阻到地和发送端串联50欧电阻,那不是相当于一个是在时钟线上并联,一个是串联到时钟线上?

5、受教。

小弟刚出来混,所以很多地方不懂,请赐教。你实在是太好学了。这本书第六章有原理解释,只有十几页。如果你需要清晰版或者中文版在本论坛都有,中文版搜“CMOS 射频”就有了。

凭我的印象,这一章介绍了以下知识点:1.基尔霍夫定律只是个近似定律 2.集总原件和分布原件的差别 3.推导无穷重复电路网络的特性(如果参加过高中物理竞赛你会觉得很眼熟) 4.推导分布式传输线“带宽可达无穷大”的特性 5.推导终端电阻等效的传输线 6.推导低频下的有损传输线

以上是原理。从实用层面,在PCB上实现的传输线有两种形式:STRIPLINE和MICROSTRIP。同一个作者的“PLANAR MICROWAVE ENGINEERING”这本书有介绍。

对于更实际的Layout Guideline,很多地方都能找到。比如Altera的这个(其实和我前一个回帖大同小异):

http://www.altera.com/literature/an/an224.pdf

谢谢大神这么热心的回答,并提供这么多的资料给我 。学习了,感谢

好贴!

标题不清楚

问题内容与有源晶振无关

实际是数字信号完整性的问题