同步器的展宽

2.展宽一般采用什么方法?

展宽数据宽度?

对的,数据宽度展宽一个慢时钟周期,但是不知道怎么实现!求指导

展宽肯定是在快时间域展,这样才能保证慢时钟能够采样到。但展宽的方法也是有条件的,一般单bit的信号可以这样做,实现方法就是让信号在快时钟域多保持一段时间,保持多久跟据快慢时钟的比例有关系。数据跨频,一般还是采用异步FIFO比较保险一些。

这个我知道,但是我不知道一般的展宽是怎样实现的,就知道需要展宽,异步FIFO我也知道,只是想了解展宽的实现。求指教

如果是单bit信号,最简单的做法就是打几拍或把这些打拍后的信号相或(高有效)或者 相与(低有效)。

输出到另外一个时钟域前最好在原时钟寄存一拍在输出

比如展宽10拍:....

if(extend_cnt==4'd9)

signal_a_ex <= 1'b0;

else if(singal_a)

signal_a_ex <= 1'b1;

......

if(extend_cnt==4'd9)

extend_cnt <= 4'b0;

else if(signal_a_ex)

extend_cnt <= extend_cnt + 1'b1;

展宽的宽度至少为慢时钟域的一个周期,如果是在快时钟域展宽,岂不是在快时钟域中引入慢时钟了?是不是应该在慢时钟域中展宽呢?

恩,要先展宽之后再做同步,举个例子,如果在100M的时钟域有一个信号,信号的宽度只有一个100M时钟周期10ns,然后希望同步到10M的时钟域,这样基本上来说,在不展宽的情况下,10MHz的时钟不会看到这个信号。当然了,如果100M时钟域的信号已经足够宽了,那么10MHz的时钟可以正常采样到,这就不需要先做展宽了。

展宽的目的就是为了让慢时钟能够看到快时钟域的信号。展宽的计数就是根据快慢时钟的比例来确定的。

我去试了试,打几拍的方法只能实现数据的延时,并不能实现数据的展宽啊。

我去试试

关于这个真的搞不懂,首先没有理解他的原理纯粹的代码,看着很难理解

打几拍过后相或可以实现高电平的展宽,相与可以实现低电平的展宽,我去做了是对的。但是这种情况是不是只能对控制信号进行展宽,对于数据信号是不能这样的吧?

我有个问题呢!展宽的设计到底应该在哪个部分?是在快时钟域,还是在慢时钟域呢?如果在慢时钟域它是在同步器之前?之后还是之间?这个真搞不懂

如果是多bit数据的跨时钟域处理的话可以考虑用异步fifo或dmux电路处理。

打几拍,再相或,然后再把或以后的信号到慢时钟域寄存

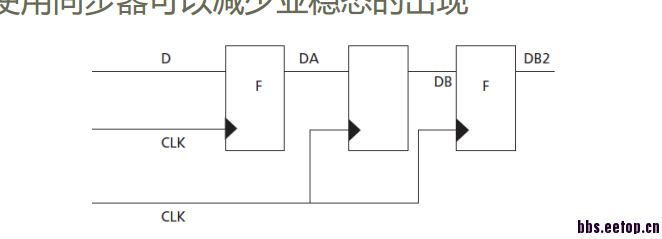

从这个电路来看就是慢时装域到快时钟域同步,如果要快到慢同步,可以把第一个寄存器扩展为一个展宽电路,如前所述,打几拍后,将各级打拍输出取或,打拍级数和两个时钟比例相关

如果是这样的话,就必须用3级同步器了?我在一份资料上看到过,在一个时钟域的寄存器与另一个时钟域的同步器的第一个触发器之间不能有组合逻辑。但是你这样说的话,就必须对展宽后的信号进行同步,展宽一个触发器,同步2个触发器就是3个触发器了,在展宽结构中有组合逻辑,这不是相互矛盾吗?

昨天在一个论坛上看到了关于展宽的解释:在已知慢时钟与快时钟关系的时候可以在快时钟采用计数器进行展宽;在未知关系的时候可以采用反馈信号进行展宽

- always @(posedge fast_clk or negedge rst_n)

- begin

- if(rst_n == 1'b0)

- fast_ext <= 8'h0;

- else

- fast_ext <= {fast_ext[6:0],fast_pls};

- end

- always @(posedge slow_clk or negedge rst_n)

- begin

- if(rst_n == 1'b0)

- begin

- pls_r1 <= 1'b0;

- pls_r2 <= 1'b0;

- pls_r3 <= 1'b0;

- end

- else

- begin

- pls_r1 <= |fast_pls;

- pls_r2 <= pls_r1;

- pls_r3 <= pls_r2;

- end

- end

- assign pls_pose = pls_r2 & (~pls_r3);

这样做是可以的,而且在FPGA很多项目里用过了,但是这样做同步的第一级有组合逻辑。你可以可以尝试在快时钟域就把脉冲延拓,然后在慢时钟域就可以纯粹2拍同步。

这个代码我下去实现了下,并不能把原数据展宽10倍,只能让原数据的高电平为时钟周期的10倍,如果原数据高电平周期为时钟周期的10倍,就不会有变化,好像在跨时钟域中这样也能保证数据的正确传输,只是说法不太对