(新手求教i)我写了一个六数码管的电子时钟,希望大家给点评点评

时间:10-02

整理:3721RD

点击:

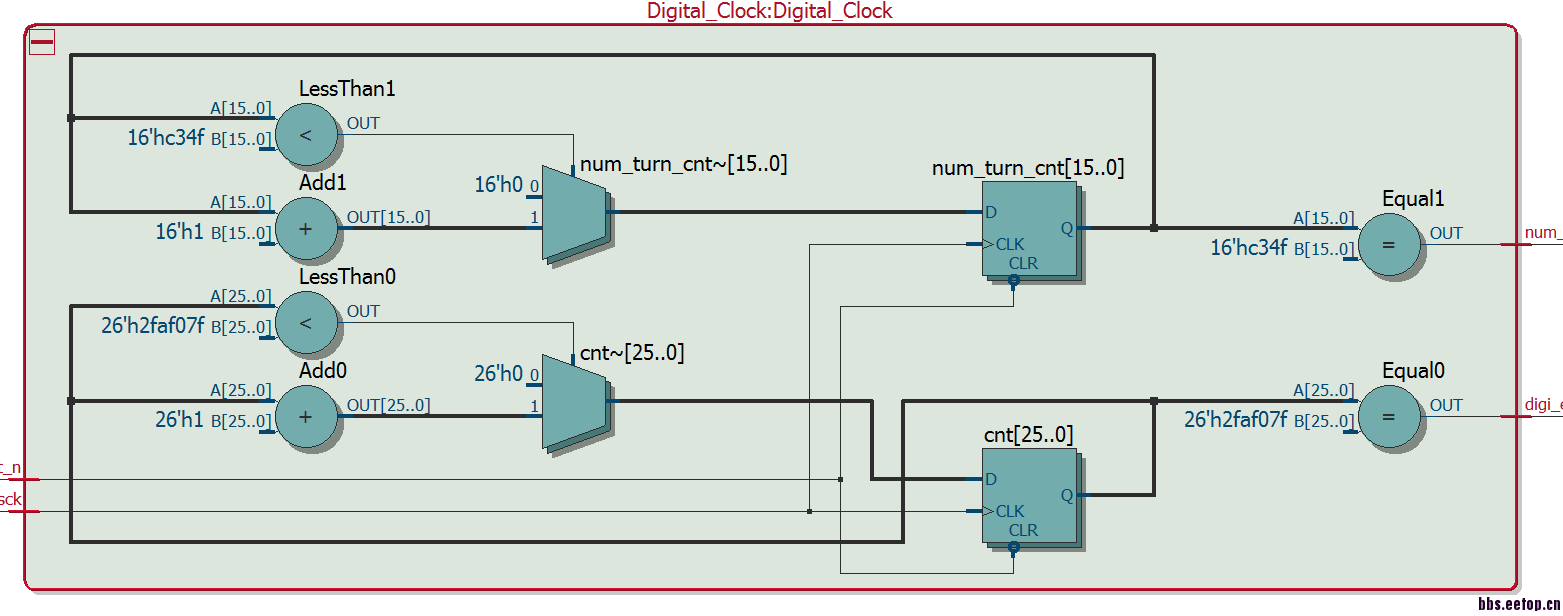

移植的C语言,功能可以实现了但是不知道这样好不好。module Digital_Clock

(

input sck,

input rst_n,

output num_turn,

output digi_en

);

reg [25:0]cnt;

reg [15:0]num_turn_cnt;

always@ (posedge sck or negedge rst_n)

begin

if(!rst_n)

begin

cnt <= 26'b0;

num_turn_cnt <= 16'b0;

end

else

begin

if(cnt<49_999_999)

cnt <= cnt+1'b1;

else

cnt <= 26'd0;

if(num_turn_cnt<49_999)

num_turn_cnt<=num_turn_cnt+1'b1;

else

num_turn_cnt<=16'd0;

end

end

assign digi_en = (cnt == 26'd49_999_999) ? 1'b1 : 1'b0;

assign num_turn = (num_turn_cnt == 16'd49_999) ? 1'b1 : 1'b0;

endmodule

module Digital_Run

(

input sck,

input rst_n,

input digi_en,

input num_turn,

output reg [3:0] LED_Data,

output reg [7:0] DIG_Data,

output reg [5:0] DIG_SEL

);

reg [2:0] timer_cnt;

reg [3:0] shi_h;

reg [2:0] fen_h;

reg [2:0] miao_h;

reg [3:0] shi_l;

reg [3:0] fen_l;

reg [3:0] miao_l;

always@ (posedge sck or negedge rst_n)

begin

if(!rst_n)

begin

DIG_Data [7:0] <= 8'h40;

DIG_SEL [5:0] <= 6'b0;

LED_Data [3:0] <= 4'b0;

timer_cnt [2:0] <= 3'b0;

shi_h [3:0] <= 4'b0;

shi_l [3:0] <= 3'b0;

fen_h [2:0] <= 3'b0;

fen_l [3:0] <= 3'b0;

miao_h [2:0] <= 3'b0;

miao_l [3:0] <= 3'b0;

end

else

begin

if(digi_en==1)

begin

LED_Data [3:0] <= LED_Data+1'b1;

if(miao_l [3:0] == 4'h9)

begin

miao_l[3:0] <= 3'b0;

if(miao_h [2:0] == 3'h5)

begin

miao_h [2:0] <= 3'b0;

if(fen_l [3:0]==4'h9)

begin

fen_l[3:0] <=4'b0;

if(fen_h[2:0]==3'h5)

begin

fen_h[2:0]<= 3'b0;

if(shi_l[3:0]==4'h9)

begin

shi_l[3:0]<=4'b0;

if(shi_h[3:0]==4'h9)

shi_h[3:0] <= 4'b0;

else

shi_h[3:0] <= shi_h[3:0]+1'b1;

end

else

shi_l[3:0] <= shi_l[3:0]+1'b1;

end

else

fen_h [2:0] <= fen_h [2:0]+1'b1;

end

else

fen_l [3:0] <= fen_l [3:0]+1'b1;

end

else

miao_h [2:0] <= miao_h [2:0]+1'b1;

end

else

miao_l [3:0] <= miao_l[3:0]+1'b1;

end

else

LED_Data [3:0] <= LED_Data [3:0];

if(num_turn==1)

begin

if(timer_cnt[2:0] == 3'b101)

timer_cnt [2:0] <= 3'b0;

else

timer_cnt [2:0] <= timer_cnt [2:0]+1'b1;

case (timer_cnt [2:0])

3'h0 :

begin

DIG_SEL [5:0] <= 6'b011111;

case(shi_h [3:0])

4'b0000 : DIG_Data [7:0] <= 8'b11000000;//显示0

4'b0001 : DIG_Data [7:0] <= 8'b11111001;//显示1

4'b0010 : DIG_Data [7:0] <= 8'b10100100;//显示2

4'b0011 : DIG_Data [7:0] <= 8'b10110000;//显示3

4'b0100 : DIG_Data [7:0] <= 8'b10011001;//显示4

4'b0101 : DIG_Data [7:0] <= 8'b10010010;//显示5

4'b0110 : DIG_Data [7:0] <= 8'b10000010;//显示6

4'b0111 : DIG_Data [7:0] <= 8'b11111000;//显示7

4'b1000 : DIG_Data [7:0] <= 8'b10000000;//显示8

4'b1001 : DIG_Data [7:0] <= 8'b10010000;//显示9

default : DIG_Data [7:0] <= 8'hff;

endcase

end

3'h1 :

begin

DIG_SEL [5:0] <= 6'b101111;

case(shi_l [3:0])

4'b0000 : DIG_Data [7:0] <= 8'b01000000;//显示0

4'b0001 : DIG_Data [7:0] <= 8'b01111001;//显示1

4'b0010 : DIG_Data [7:0] <= 8'b00100100;//显示2

4'b0011 : DIG_Data [7:0] <= 8'b00110000;//显示3

4'b0100 : DIG_Data [7:0] <= 8'b00011001;//显示4

4'b0101 : DIG_Data [7:0] <= 8'b00010010;//显示5

4'b0110 : DIG_Data [7:0] <= 8'b00000010;//显示6

4'b0111 : DIG_Data [7:0] <= 8'b01111000;//显示7

4'b1000 : DIG_Data [7:0] <= 8'b00000000;//显示8

4'b1001 : DIG_Data [7:0] <= 8'b00010000;//显示9

default : DIG_Data [7:0] <= 8'hff;

endcase

end

3'h2 :

begin

DIG_SEL [5:0] <= 6'b110111;

case(fen_h [2:0])

4'b0000 : DIG_Data [7:0] <= 8'b11000000;//显示0

4'b0001 : DIG_Data [7:0] <= 8'b11111001;//显示1

4'b0010 : DIG_Data [7:0] <= 8'b10100100;//显示2

4'b0011 : DIG_Data [7:0] <= 8'b10110000;//显示3

4'b0100 : DIG_Data [7:0] <= 8'b10011001;//显示4

4'b0101 : DIG_Data [7:0] <= 8'b10010010;//显示5

4'b0110 : DIG_Data [7:0] <= 8'b10000010;//显示6

4'b0111 : DIG_Data [7:0] <= 8'b11111000;//显示7

4'b1000 : DIG_Data [7:0] <= 8'b10000000;//显示8

4'b1001 : DIG_Data [7:0] <= 8'b10010000;//显示9

default : DIG_Data [7:0] <= 8'hff;

endcase

end

3'h3 :

begin

DIG_SEL [5:0] <= 6'b111011;

case(fen_l [3:0])

4'b0000 : DIG_Data [7:0] <= 8'b01000000;//显示0

4'b0001 : DIG_Data [7:0] <= 8'b01111001;//显示1

4'b0010 : DIG_Data [7:0] <= 8'b00100100;//显示2

4'b0011 : DIG_Data [7:0] <= 8'b00110000;//显示3

4'b0100 : DIG_Data [7:0] <= 8'b00011001;//显示4

4'b0101 : DIG_Data [7:0] <= 8'b00010010;//显示5

4'b0110 : DIG_Data [7:0] <= 8'b00000010;//显示6

4'b0111 : DIG_Data [7:0] <= 8'b01111000;//显示7

4'b1000 : DIG_Data [7:0] <= 8'b00000000;//显示8

4'b1001 : DIG_Data [7:0] <= 8'b00010000;//显示9

default : DIG_Data [7:0] <= 8'hff;

endcase

end

3'h4 :

begin

DIG_SEL [5:0] <= 6'b111101;

case(miao_h [2:0])

4'b0000 : DIG_Data [7:0] <= 8'b11000000;//显示0

4'b0001 : DIG_Data [7:0] <= 8'b11111001;//显示1

4'b0010 : DIG_Data [7:0] <= 8'b10100100;//显示2

4'b0011 : DIG_Data [7:0] <= 8'b10110000;//显示3

4'b0100 : DIG_Data [7:0] <= 8'b10011001;//显示4

4'b0101 : DIG_Data [7:0] <= 8'b10010010;//显示5

4'b0110 : DIG_Data [7:0] <= 8'b10000010;//显示6

4'b0111 : DIG_Data [7:0] <= 8'b11111000;//显示7

4'b1000 : DIG_Data [7:0] <= 8'b10000000;//显示8

4'b1001 : DIG_Data [7:0] <= 8'b10010000;//显示9

default : DIG_Data [7:0] <= 8'hff;

endcase

end

default :

begin

DIG_SEL [5:0] <= 6'b111110;

case(miao_l [3:0])

4'b0000 : DIG_Data [7:0] <= 8'b11000000;//显示0

4'b0001 : DIG_Data [7:0] <= 8'b11111001;//显示1

4'b0010 : DIG_Data [7:0] <= 8'b10100100;//显示2

4'b0011 : DIG_Data [7:0] <= 8'b10110000;//显示3

4'b0100 : DIG_Data [7:0] <= 8'b10011001;//显示4

4'b0101 : DIG_Data [7:0] <= 8'b10010010;//显示5

4'b0110 : DIG_Data [7:0] <= 8'b10000010;//显示6

4'b0111 : DIG_Data [7:0] <= 8'b11111000;//显示7

4'b1000 : DIG_Data [7:0] <= 8'b10000000;//显示8

4'b1001 : DIG_Data [7:0] <= 8'b10010000;//显示9

default : DIG_Data [7:0] <= 8'hff;

endcase

end

endcase

end

end

end

endmodule

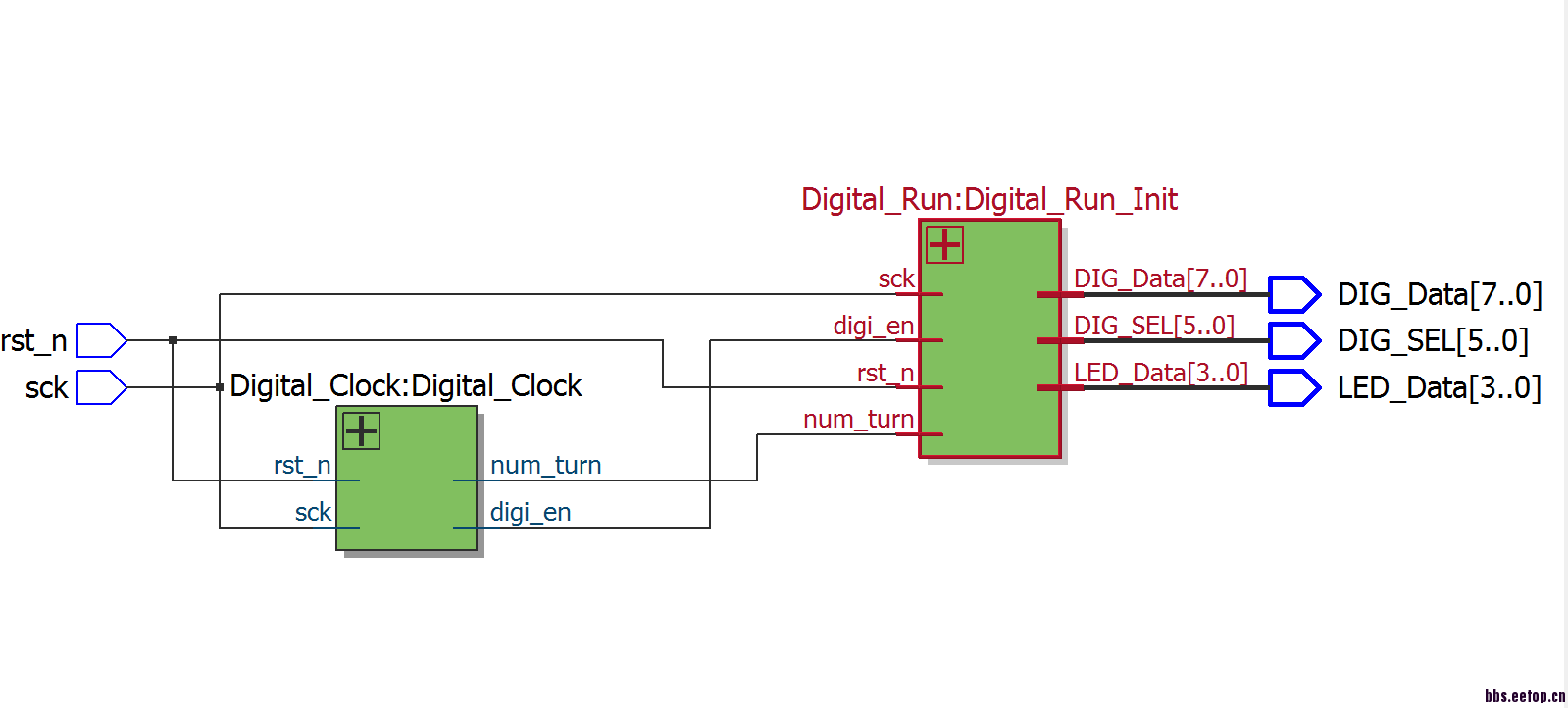

module Digital_pipe

(

input sck,

input rst_n,

output [3:0] LED_Data,

output [7:0] DIG_Data,

output [5:0] DIG_SEL

);

wire digi_en;

Digital_Clock Digital_Clock

(

.sck (sck),

.rst_n (rst_n),

.num_turn (num_turn),

.digi_en (digi_en)

);

Digital_Run Digital_Run_Init

(

.sck (sck),

.rst_n (rst_n),

.digi_en (digi_en),

.num_turn (num_turn),

.LED_Data (LED_Data),

.DIG_Data (DIG_Data),

.DIG_SEL (DIG_SEL)

);

endmodule

[attach]623712[/attach]

[attach]623712[/attach]

代码写得真心不好,建议你看看点拨FPGA的第13章,怎么设计电子时钟讲得非常详细

不要这么打击新人嘛。

啊的都是

都是啥?

Verilog快忘完了,为啥不用VHDL,严谨些

Thắng cảm ơn

都说VHDL难学。