开始用fpga写adc 100M 8bit 数据采集控制器

时间:10-02

整理:3721RD

点击:

开始先写一个adc的控制模块,大家帮帮忙看看!后面的再说。

module adc_save(clk,ioclk,datain,pd,rst_n);

input clk,rst_n;

input [7:0]datain;

output ioclk,pd;

reg ioclk,pd;

//reg [7:0]count;

reg [3:0]cnt;

reg [7:0]data_t;//temp_data

///////////////////initial

///////////////////

assign ioclk=clk;

always (posedge ioclk,negedge ioclk,negedge rst_n)

begin

if (!rst_n)

begin

pd<=0;

cnt<=0;

state<=sample;

end

case(state)

sample:

begin

if (!ioclk)

begin data_t<=datain;state<=save;end

else begin state<=sample; end

end

save:

begin

if (ioclk)

begin

...

end

end

end

endmodule

第一个问题,我晶振是50M的,io口需要一个50MHZ的时钟信号,能不能用assign clkio=clk;阿?

要不加个OBUF?

回复得信元

小编好人,谢谢

实验室的女生,伤不起阿!adc的控制不难,但是与fifo结合起来就有点麻烦!控制部分时序我贴出来了。fifo存储部分还在看,希望有大神帮忙呢!感激不尽阿

]

module adc_save(clk,ioclk,datain,pd,rst_n);

input clk,rst_n;

input [7:0]datain;

output ioclk,pd;

reg ioclk,pd;

//reg [7:0]count;

reg [3:0]cnt;

reg [7:0]data_t;//temp_data

///////////////////initial

///////////////////

assign ioclk=clk;

always (posedge ioclk,negedge ioclk,negedge rst_n)

begin

if (!rst_n)

begin

pd<=0;

cnt<=0;

state<=sample;

end

case(state)

sample:

begin

if (!ioclk)

begin data_t<=datain;state<=save;end

else begin state<=sample; end

end

save:

begin

if (ioclk)

begin

...

end

end

end

endmodule

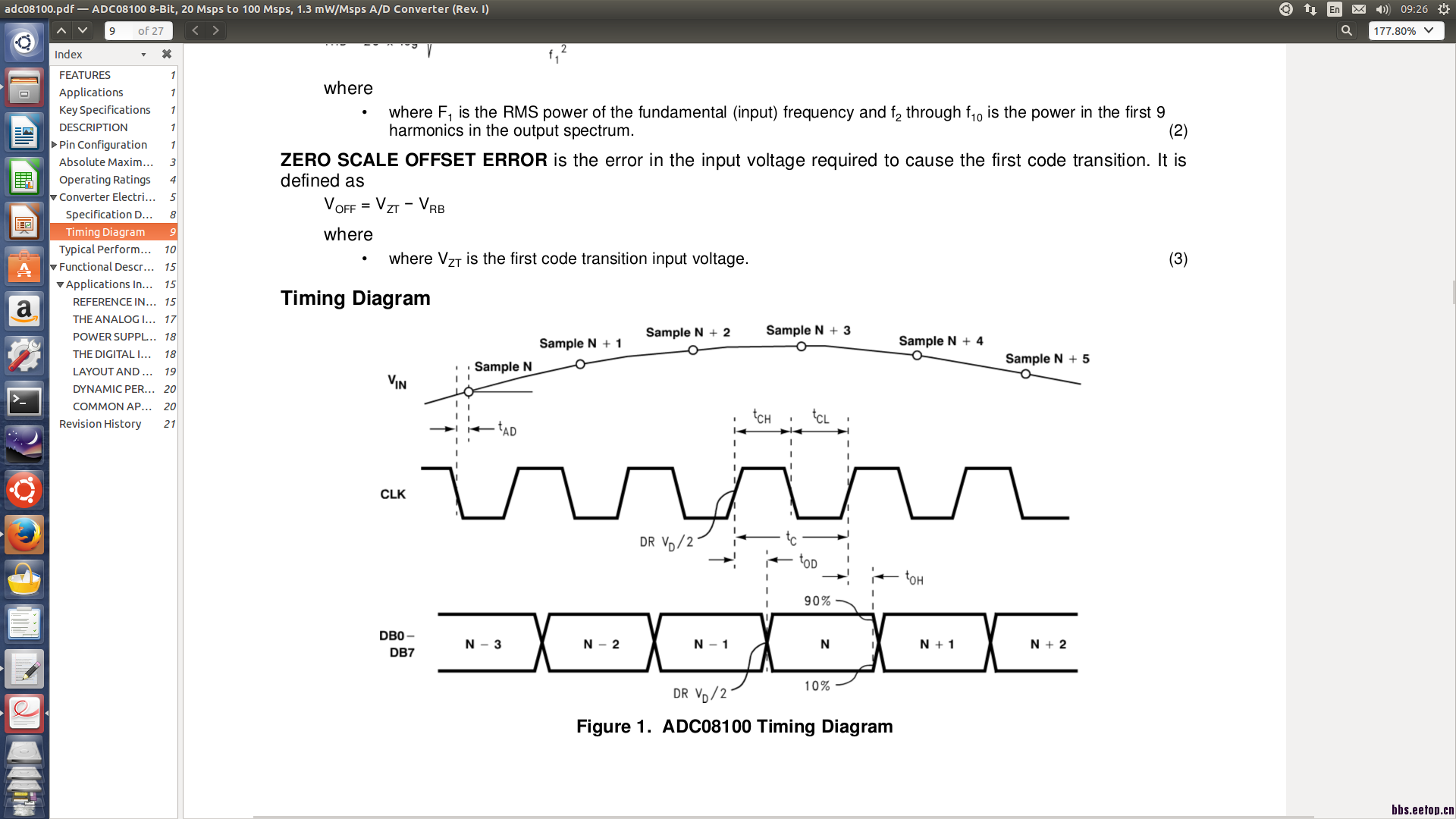

ADC的时钟从哪里来的,要注意以下时钟同步的问题

adc 的时钟,就是阿!assign ioclk=clk ,(50MHZ)

能不能用看你PCB是怎么做的,如果你把ADC的CLK接到了FPGA上那就可以这么用,不过最好是用PLL搞一下,这样相位会比较好弄

谢谢楼上。

是接到fpga的io上的。感觉用pll一下,相位考虑的好点。程序的健壮性好点。

为什么要用FIFO缓数据?要做不同时钟频率的数据读写吗?

恩,这两天出去的,没写程序。传过来的数据,要送给dsp处理。知道dsp core的处理速度,没那么快呢!