需要的时钟低于PLL和DCM所能产生的最低频率,请问我这样设计是否可行?

时间:10-02

整理:3721RD

点击:

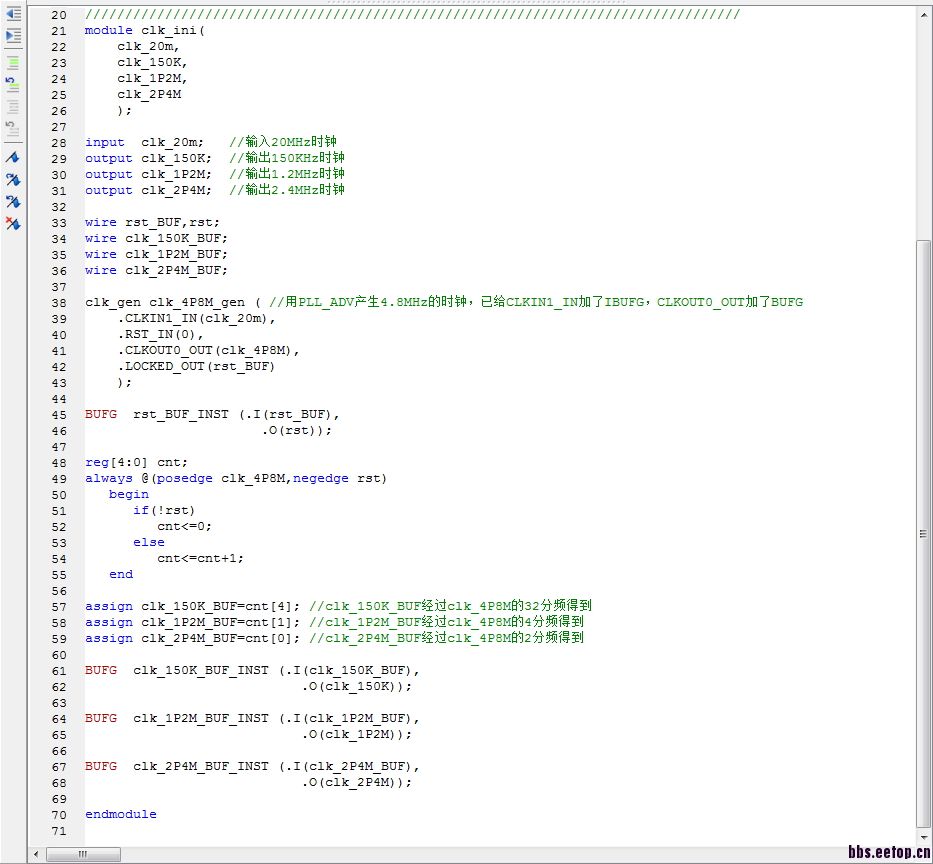

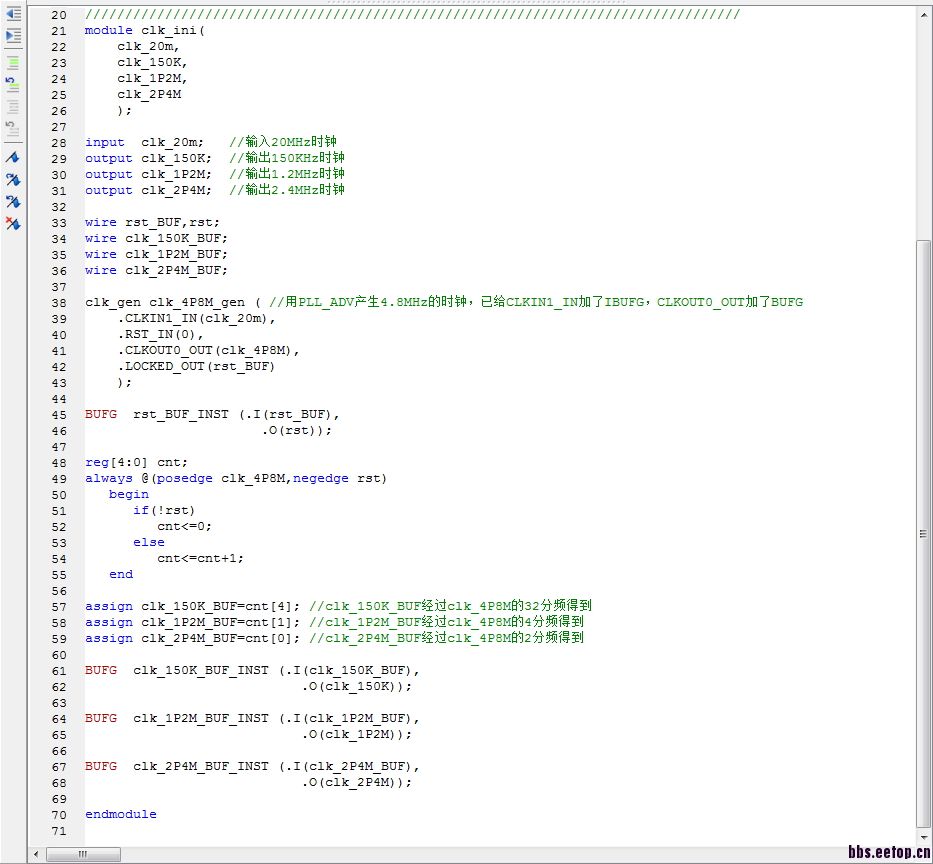

我需要3个时钟,分别为150KHz,1.2MHz和2.4MHz,单用PLL和DCM都无法得到,于是我先用PLL生成了4.8MHz的时钟,再对这4.8MHz进行分频,来得到150KHz,1.2MHz和2.4MHz, 请问这样实际可以吗? 附代码:

试试DDS。

可以,这么低的时钟对FPGA来讲基本没什么问题,或者你统一用4.8M的时钟

用DDS解决问题

多谢~

DDS产生是正弦波,我想要的是时钟信号,由正弦波再转方波?是这个思路吗?

也许真的因为频率够低,用分频时钟没问题