xilinx的除法器不能一个时钟周期得到结果?

时间:10-02

整理:3721RD

点击:

最近在把一个CycloneII上的设计移植到Xilinx片子上

发现xilinx生成的除法器IP怎么要N个周期才能得到结果?

Altera的是可选的,最小的一个周期就可以得到结果啊

这相差也太大了吧 没法移植了

发现xilinx生成的除法器IP怎么要N个周期才能得到结果?

Altera的是可选的,最小的一个周期就可以得到结果啊

这相差也太大了吧 没法移植了

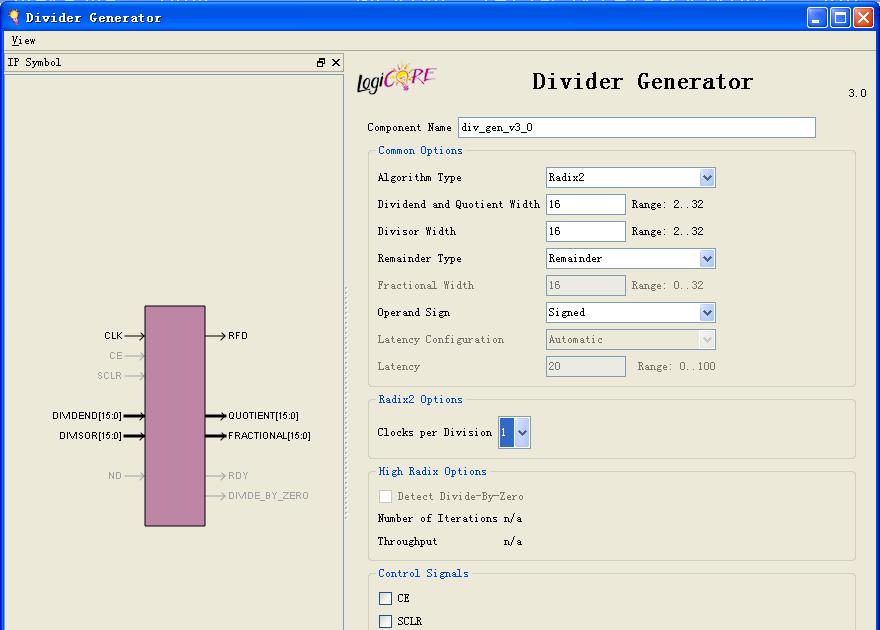

是你还不会用工具吧,朋友,见下图

clock per division选项难道不是?

要么就是你用modelsim仿真不正确,数错了

clock per division选项难道不是?要么就是你用modelsim仿真不正确,数错了

那个latency的意思是不是每次除法结果要延迟20个周期才出来?

2# loveineda

在使用ISE的时候,发现有两个可以生产乘法器的核,请问该选哪种啊?

谢了。

又学了一手。

不错,了解了

一个时钟出一个数没有问题, 我用过, 不过延时肯定不会是一个时钟周期, 跟参与除法的数据位数有关系.

乘法器的话, 最简单的就是直接在程序中用 * 就可以了, 如果要用核, 可以选用DSP48E来实现(不占slice资源)

我想问一下 1# 你的除法器是不是已经弄出来了啊 只有一个时钟延迟输出数据 !

我做的也一样 都是在被除数的位数 + 2 个时钟才输出第一个数据啊

您好,请教您一下,我最近项目中就是用ipcore生成了一个32bit除以32bit的除法器,radix2,clock per选择的是1,结果在map的时候时间很长过不去,困扰好几天了,不知道您有什么好的解决方法没?

ISE是每个时钟周期进行一次除法运算,但是结果要延迟20个周期才出来;而Quartus是延迟一个周期出来。是这样子的吗?

可以的,流水输出。

LZ搞清楚没?,我也遇到这样问题了,不过是延时 除数位数+3 个周期,才出结果