懂Verilog的请戳进来看一下 帮帮忙

Verilog小白一个,老师要求把RR-FSM的电路用代码写出来并综合,改了多次还是没改对,请问有没有大牛写过这个代码发发来看看 checker用的是奇偶校验 下面的是我的代码 就是不知道奇偶校验码k怎么产生 而且怎么才能综合

`timescale 1ns/1ps

module fsm_example (din,rst_n,clk,

vout);

input din, rst_n, clk;

output vout;

reg vout,q,R3;

reg[1:0] R1,R2,R0;

reg[0:0] k;

reg[2:0] a;

reg [1:0] next_state,current_state;

parameter [1:0] NONE = 2'b00;

parameter [1:0] SINGLE = 2'b01;

parameter [1:0] DOUBLE = 2'b11;

always @ (posedge clk or negedge rst_n)

if (!rst_n)

begin

current_state <= NONE;

end

else

begin

R0<= next_state;R1<=R0;

R3<=q; R2<=R1;

end

always@(R0)begin

a={R0[1:0],k[0:0]};q=^a;end

always@(posedge clk or R0 )

if(R3)

current_state<=R2;

else

current_state<=R0;

always @ (din or current_state)

case (current_state)

NONE:

if (din )

next_state = SINGLE;

else

next_state = current_state;

SINGLE:

if (din )

next_state = DOUBLE;

else

next_state = NONE;

DOUBLE:

if (din )

next_state = current_state;

else

next_state = NONE;

default:

next_state = current_state;

endcase

always @ (current_state)

case (current_state)

NONE : vout = 1'b0;

SINGLE : vout = 1'b0;

DOUBLE : vout = 1'b1;

default: vout = 1'b0;

endcase

endmodule

没有写过类似的代码,但是看到下面的代码就觉得不对。

我猜你想表达的是一个DFF,但是这种写法无论是FPGA和ASIC综合器都很难识别。

always@(posedge clk or R0 )

if(R3)

current_state<=R2;

else

current_state<=R0;

那应该怎么写我今天又改成这个样子 always@(R3 or R0 )if(R3)

current_state=R2;

else

current_state=R0;

你应该说的是这个写法是不对的 那你可不可以告诉我 可以怎么写即能实现上面功能又能综合 谢谢 用case代替if?

这个有限状态机好奇怪啊,R3和R0运算,要得到什么? 怎么会有这样的电路,出题目的人好任性的说!

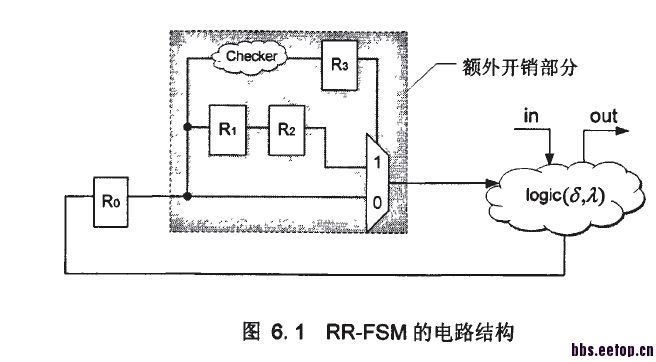

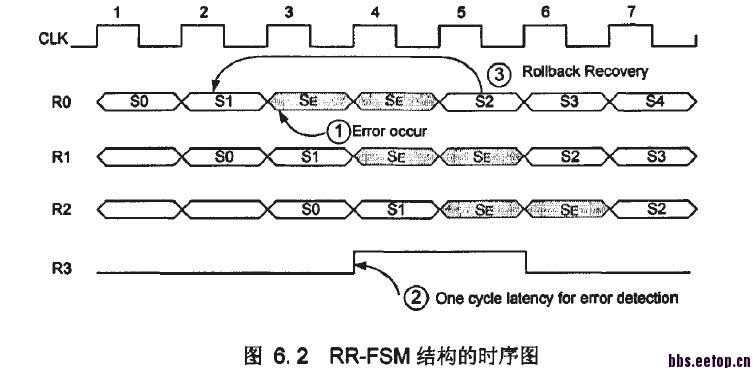

哈哈,又仔细看了一下,才明白,原来出题人是硬编码了一个ERROR状态的ROLLBACK机制,这个就直接把电路图转换成VERILOG就好了,再写状态机你就错了

我差不多什么都不懂 硬翻书写的 错不错我都不知道 我的代码需要什么纠正的吗

说实话我正在做毕业设计 做仿真方面我必须要把状态机写出来 不是单单写个电路就能交差的 仿真我已经做出来了 就是不能综合出电路 能不能帮我看看哪里出问题了

按照6.1直接把原理图转换成verilog或者按照6.2写一个检测到错误就转到s1状态的状态机, 6.1就是状态转移图的硬编码方式,和直接写状态机方式综合后应该差不多。

你的问题是verilog基础知识,而不是仅仅这个状态机的编写,建议好好学习一下verilog语言,多看几个状态机程序的例子。

我的问题已经解决了 谢谢大家