板级调试时,rom读不出数据

时间:10-02

整理:3721RD

点击:

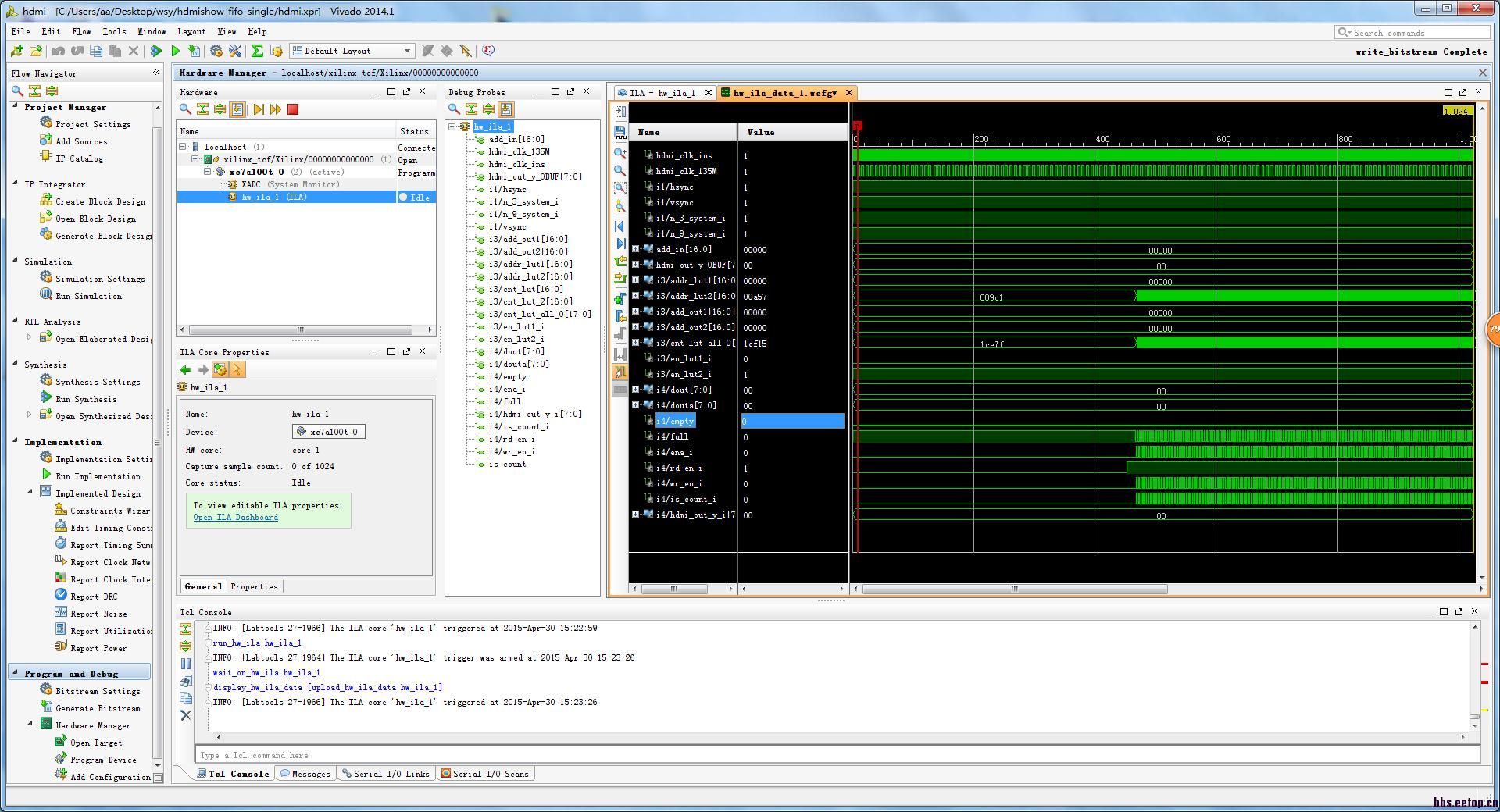

用的是vivado2014.1,直接调用ip核例化rom,也导入了coe文件,在vivado里仿真的时候rom都好好的,可以读出数据,但是烧到板子里的时候就读不出数据来,请大侠帮忙一下,哪里出问题了?

i3/addr_lut1是给查找表lut1ROM的地址 ;i3/en_lut1_i是给查找表lut1ROM的使能 ;i3/add_out1是查找表lut1ROM的输出 ;

i3/addr_lut2是给查找表lut2ROM的地址; i3/en_lut2_i是给查找表lut2ROM的使能 ;i3/add_out2是查找表lut2ROM的输出 ;

rom都是给54M时钟

module unfold(

rst,

clk_g,//54M

clk_100M,

add_out1,

add_out2,

is_count

);

//----------------------------------------------------port declare

input rst;

input clk_g;

input clk_100M;

input is_count;

output [16:0] add_out1;

output [16:0] add_out2;

//-------------------------------------------------------------add for lut

(*mark_debug = "true"*) reg [16:0] cnt_lut; //(*mark_debug = "true"*)

(*mark_debug = "true"*) reg [17:0] cnt_lut_all; // (*mark_debug = "true"*)

(*mark_debug = "true"*) reg en_lut1_i; // (*mark_debug = "true"*)

(*mark_debug = "true"*) reg en_lut2_i; //(*mark_debug = "true"*)

always @(posedge clk_g or negedge rst)

begin if (!rst) cnt_lut <= 17'b0;

else if (cnt_lut == 17'd103679) cnt_lut <= 17'b0;

else if (is_count) cnt_lut <= cnt_lut + 1'b1;

end

always @(posedge clk_g or negedge rst)

begin if (!rst) cnt_lut_all <= 18'b0;

else if (cnt_lut_all == 18'd207359) cnt_lut_all <= 18'b0;

else if (is_count) cnt_lut_all <= cnt_lut_all +1'b1;

end

//-------------------------------------------------------------------assign lut en

always @(posedge clk_100M or negedge rst)

begin if (!rst) begin en_lut1_i <= 1'b0; en_lut2_i <= 1'b0; end

else if(cnt_lut_all < 18'd103679)

begin en_lut1_i <= 1'b1; en_lut2_i <= 1'b0;end //flag1 <= 1'b1;flag2 <= 1'b0;

else if(cnt_lut_all>18'd103679 && cnt_lut_all<=18'd207359)

begin en_lut1_i <= 1'b0;en_lut2_i <= 1'b1;end

else if (!is_count) begin en_lut1_i <= 1'b0; en_lut2_i <= 1'b0; end

end

wire en_lut2;

wire en_lut1;

assign en_lut1 = en_lut1_i;

assign en_lut2 = en_lut2_i;

//----------------------------------------------------------------- assign lut addr

(*mark_debug = "true"*) wire [16:0] addr_lut2; //(*mark_debug = "true"*)

(*mark_debug = "true"*) wire [16:0] addr_lut1;// (*mark_debug = "true"*)

assign addr_lut1=(en_lut1_i)?cnt_lut:17'b0;

assign addr_lut2=(en_lut2_i)?cnt_lut:17'b0;

//----------------------------------------------------------------- assign add and en to odd img rom or even img rom

//------------------------------------------------------------lut1

wire clk_lut1 = clk_g;

//(*mark_debug = "true"*)

(*mark_debug = "true"*) wire [16:0] dout_lut1;

lut1 check1 (

.clka(clk_lut1),

.ena(en_lut1),

.addra(addr_lut1),

.douta(dout_lut1)

);

//------------------------------------------------------------lut2

wire clk_lut2 = clk_g; //(*mark_debug = "true"*)

(*mark_debug = "true"*) wire [16:0] dout_lut2;

lut2 check2 (

.clka(clk_lut2),

.ena(en_lut2),

.addra(addr_lut2),

.douta(dout_lut2)

);

////////////////////////////////////////////////////////////////////////////////////////////

reg [16:0] add_out_i1;

reg [16:0] add_out_i2;

always @(posedge clk_100M or negedge rst )

begin if (!rst) begin add_out_i1 <= 17'b0;add_out_i2 <= 17'b0;end

else if (en_lut1_i && !en_lut2_i) //rst &&

add_out_i1 = dout_lut1;

else if (!en_lut1_i&& en_lut2_i)

add_out_i2 = dout_lut2;

end

(*mark_debug = "true"*) wire [16:0]add_out1;

(*mark_debug = "true"*) wire [16:0]add_out2;

assign add_out1 = (en_lut1_i)?add_out_i1:17'b0;

assign add_out2 = (en_lut2_i)?add_out_i2:17'b0;

endmodule