求助:后仿,出现点问题,求懂得后仿的大神,给指点讨论,本人在读硕士,水平有限

ISE调用modelsim,做后仿真,出现点问题,自己以前没做过后仿真,水平有限,求大神讨论:

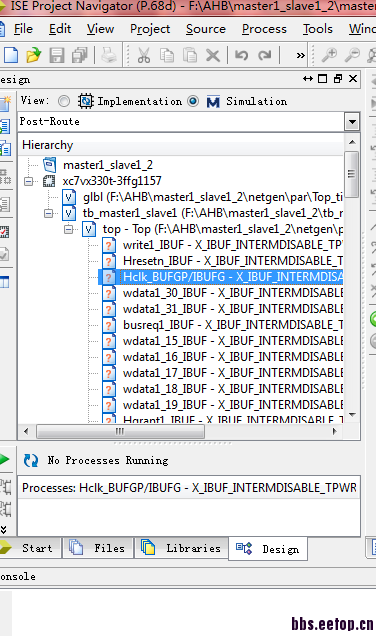

问题描述:为什么会出现许多带问题的文件,ibuf文件 是什么文件? 是没添加上么? 改怎么解决?

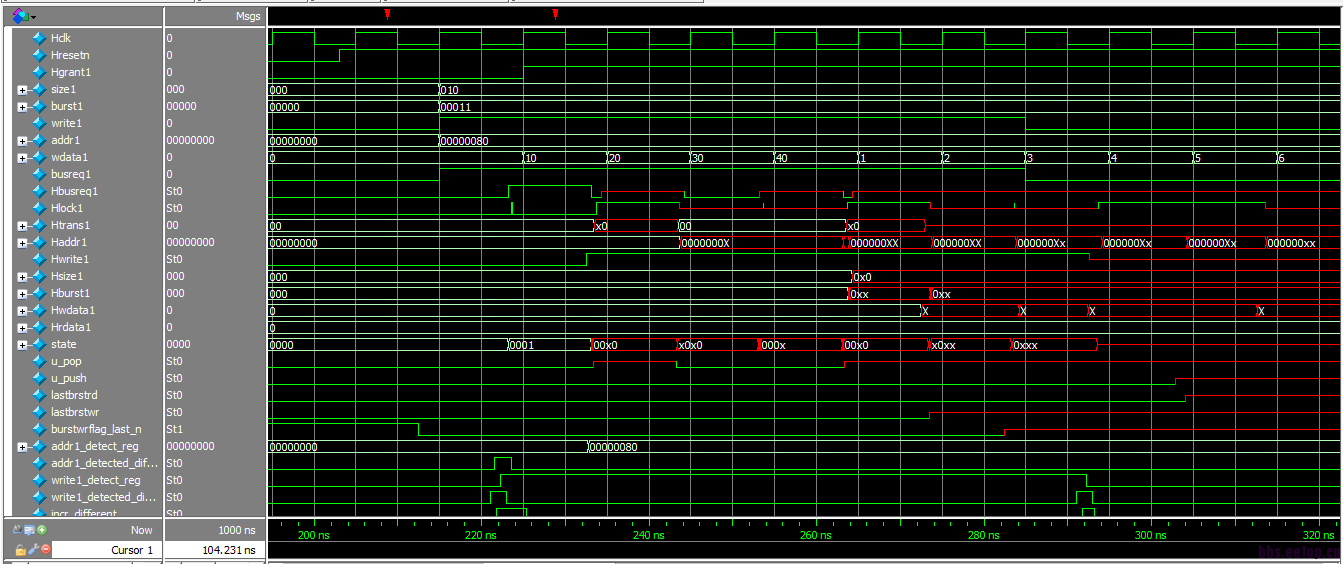

问题描述:1 为什么会在仿真波形上出现俩个三角号,什么原因引起的?

2 仿真过程中为什么会,会出现这么多红色的线,而且,还有X数据?

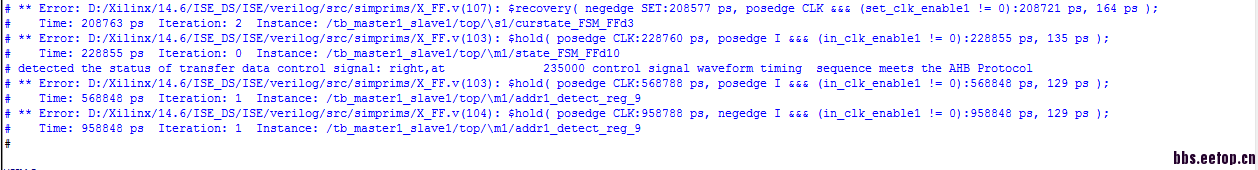

modelsim transcript 窗口出现问题显示:

问题描述:transcript 窗口显示:1,“$recovery” 出现问题,请问这是什么,改怎么解决? 之后又显示 curstate_FSM_FFd3有问题,咋回事?

2,“$hold”保持时间有问题,请问这是什么原因引起的,之后又提示 state_FSM_FFd10 和 addr1_detect_reg_9 ,该怎么解决呢?

本人水平有限,目前在做说是毕设关键时期,怎么解决这些问题,只有后仿通过,才能做fpga上板验证,可是这些问题怎么解决,以前没做过

求大神给指点讨论

设计先把约束写全,保证静态时序分析都能通过。

后仿真不是必须步骤。

在ISE的安裝路徑下 ./ISE/verilog/src/simprims,可找到你需要的X_* cell。

功能和时序可以靠形式验证和STA替代后仿步骤,但是有些还是替代不了,PLL,异步复位,X传播,跨时域,FIFO什么的,STA是替代不了的

說的對

设计里 主要有一些状态机,状态机 都是三段式编写的,还有一些 由状态机的状态和一些信号 利用组合逻辑,作为在 if else 的条件判断语句,之后 slave1 模块中,自己建立了个 reg [31:0] memory [0:65535]; 之后在做后仿真时 报告出这么几个问题:

1 WARNING:Xst:2170 - Unit master1 : the following signal(s) form a combinatorial loop:

lastbrstwr, nstate<2>, u_pop_Hwrite1_AND_37_o, nstate[3]_GND_2_o_equal_117_o,

lastbrstwr_lastbrstrd_OR_46_o, nstate<0>, nstate[3]_Hresp1[1]_AND_32_o.

2 WARNING:Xst:1710 - FF/Latch <Htrans1_0> (without init value) has a constant value of 0 in block <m1>. This FF/Latch will be trimmed during the optimization process.

3 WARNING:Xst:1710 - FF/Latch <Hresp1_1> (without init value) has a constant value of 0 in block <s1>. This FF/Latch will be trimmed during the optimization process.

4 WARNING:Xst:2404 - FFs/Latches <Hresp1<1:1>> (without init value) have a constant value of 0 in block <slave1>.

5 WARNING:Xst:1710 - FF/Latch <Htrans1_0> (without init value) has a constant value of 0 in block <master1>. This FF/Latch will be trimmed during the optimization process.

6 后仿仿真波形中,状态机,有几个状态 完全不是 我在设计中,所要的,我真不知道 是什么原因。

大神们,这几天 我都快崩溃啦 咋整 求指导

xuexixuexi

静态时序分析,我完全不会看哈,打开过,不知道 看什么样的参数,我们实验室的 也没有会看的,不知道 里面参数 有什么具体物理含义。周期约束 和 管脚约束 在什么地方做? 意思是说 在ise中 哪里做? 是结合我选择具体的器件做么? 还怎么做? 我完全不知道 求指导

做完周期约束和管脚约束之后,我用跑 后仿真么? 还是做什么? 求指导

静态时序分析,我完全不会看哈,打开过,不知道 看什么样的参数,我们实验室的 也没有会看的,不知道 里面参数 有什么具体物理含义。周期约束 和 管脚约束 在什么地方做? 意思是说 在ise中 哪里做? 是结合我选择具体的器件做么? 还怎么做? 我完全不知道 求指导

做完周期约束和管脚约束之后,我用跑 后仿真么? 还是做什么? 求指导

哥哥,你加我qq吧 方便问题讨论,放心 我绝对不会骚扰你的! qq: 712388678

静态时序分析,我完全不会看哈,打开过,不知道 看什么样的参数,我们实验室的 也没有会看的,不知道 里面参数 有什么具体物理含义。

周期约束 和 管脚约束 在什么地方做? 意思是说 在ise中 哪里做? 是结合我选择具体的器件做么? 还怎么做? 我完全不知道 求指导

做完周期约束和管脚约束之后,我用跑 后仿真么? 还是做什么? 求指导

哥哥,你加我qq吧 方便问题讨论,放心 我绝对不会骚扰你的!

qq: 712388678