利用DSP builder在FPGA上实现FIR,使用signalTapII进行硬件测试遇到问题

时间:10-02

整理:3721RD

点击:

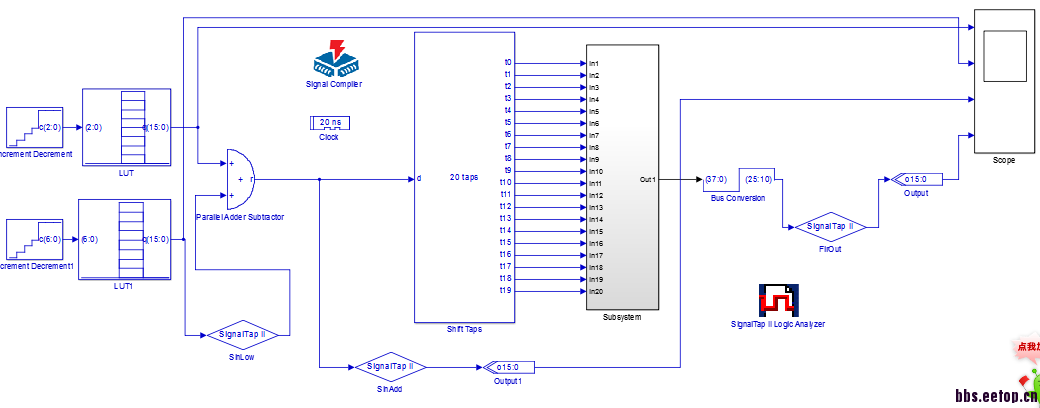

使用DSP builder搭建FIR滤波器的模型,仿真后没有问题,之后想进行硬件测试,搭建了如下的测试文件

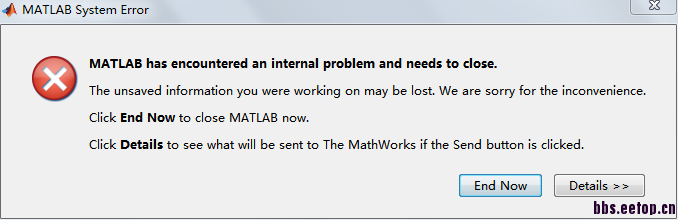

运行signal compiler生成相应的vhdl文件,之后配置引脚下载到DE2开发板中,用SignalTap II Logic Analyzer获取信号时matlab发生如下系统错误

,不知道怎么回事,然后点击提示框的叉叉matlab就自动关闭了。有没有人遇到类似的情况。

,不知道怎么回事,然后点击提示框的叉叉matlab就自动关闭了。有没有人遇到类似的情况。

要是哪位知道怎么回事的可以加我QQ:1765319923,求指导。多谢

看看,学习一下!

跑FFT的时候也遇到过,FAE说是内存不够导致的。

那你后来解决了么,是不是采样深度改小些,少采一些点就能行?感觉256的采样深度也不大啊,我是看一个资料上的指导进行仿真的,资料能出来结果。