SPI—slave模式,时序分析问题,急!求助!在线等!(刚发的那帖子貌似图挂了)

时间:10-02

整理:3721RD

点击:

最近在弄一个SPI-Slave模块,写的比较简单。但跑仿真send data模式时序没问题,receive data模式问题却很奇怪。下图是receive data模式的代码

,写的比较简单,用一个2位的移位寄存器存放MOSI,然后在SCK上升沿把MOSI的高位顺次移位给到rx_fifo[7:0]的低位,当1个字节传完,byte_rcved标志位使能,把rx_fifo中数据输出给byte_data_rcved,完成一次receive data操作。

,写的比较简单,用一个2位的移位寄存器存放MOSI,然后在SCK上升沿把MOSI的高位顺次移位给到rx_fifo[7:0]的低位,当1个字节传完,byte_rcved标志位使能,把rx_fifo中数据输出给byte_data_rcved,完成一次receive data操作。

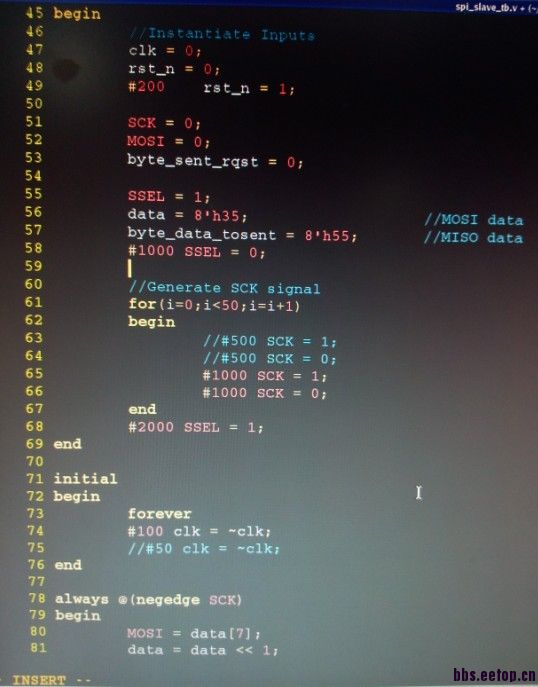

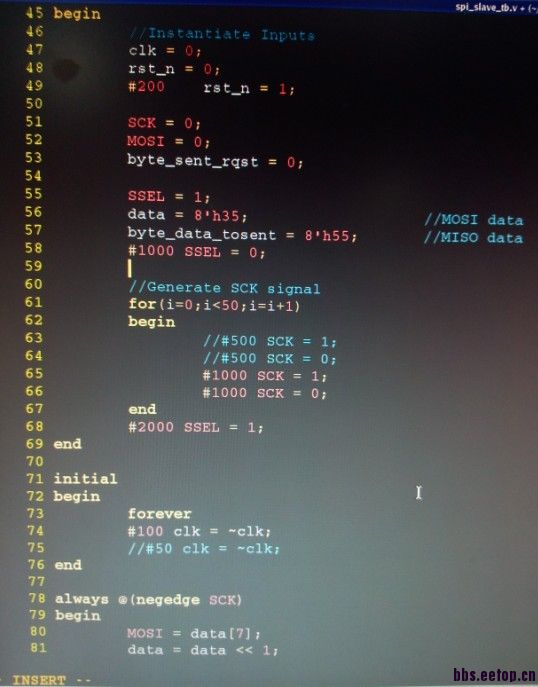

这个是testbench,

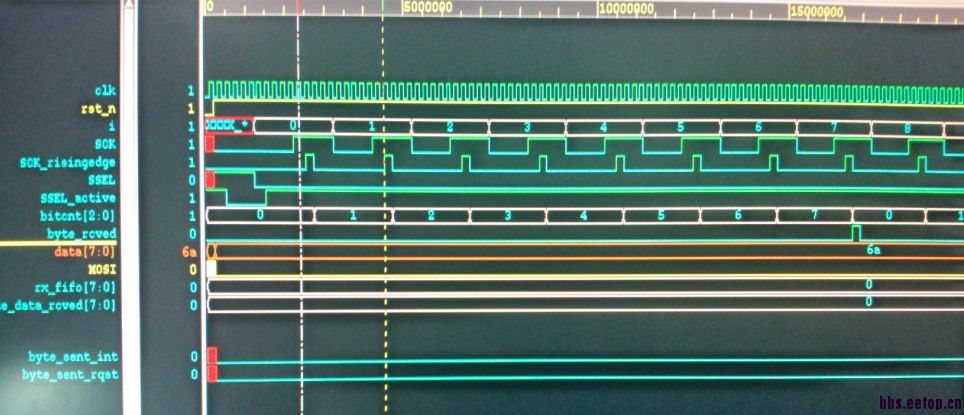

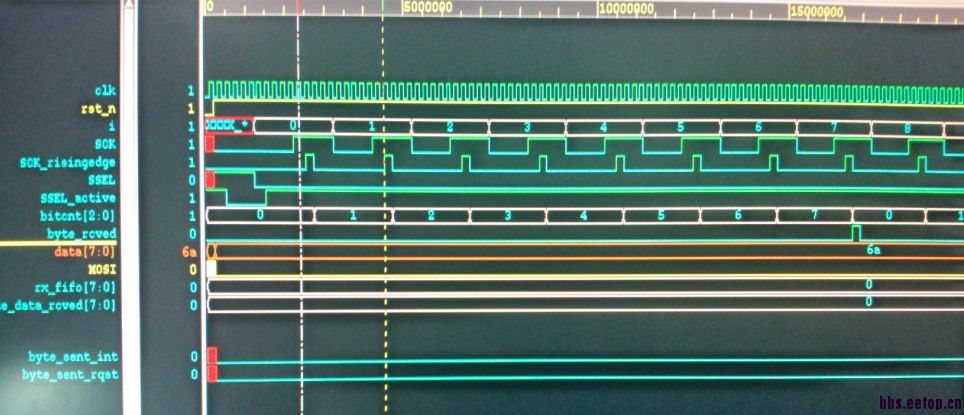

下面的问题就比较蛋疼了,看这张receive dat5a的波形图,

。如tb中,MOSI的输入数据 data[7:0] 赋值为35h,但显示到波形就变成了6Ah(也就是data[7:0]左移一位后的数值),反复试验多次都是这个问题(比如输入FF,显示为FE;输入55,显示为AA;输入77,显示为EE)。反复查看过模块代码和tb代码,还是没有头绪,蛋疼!然后MOSI信号线上输出的数据也不对(对的话应该是data[7]的从高位开始顺次输出),rx_fifo和byte_data_rcved的值也是时对时不对。

。如tb中,MOSI的输入数据 data[7:0] 赋值为35h,但显示到波形就变成了6Ah(也就是data[7:0]左移一位后的数值),反复试验多次都是这个问题(比如输入FF,显示为FE;输入55,显示为AA;输入77,显示为EE)。反复查看过模块代码和tb代码,还是没有头绪,蛋疼!然后MOSI信号线上输出的数据也不对(对的话应该是data[7]的从高位开始顺次输出),rx_fifo和byte_data_rcved的值也是时对时不对。

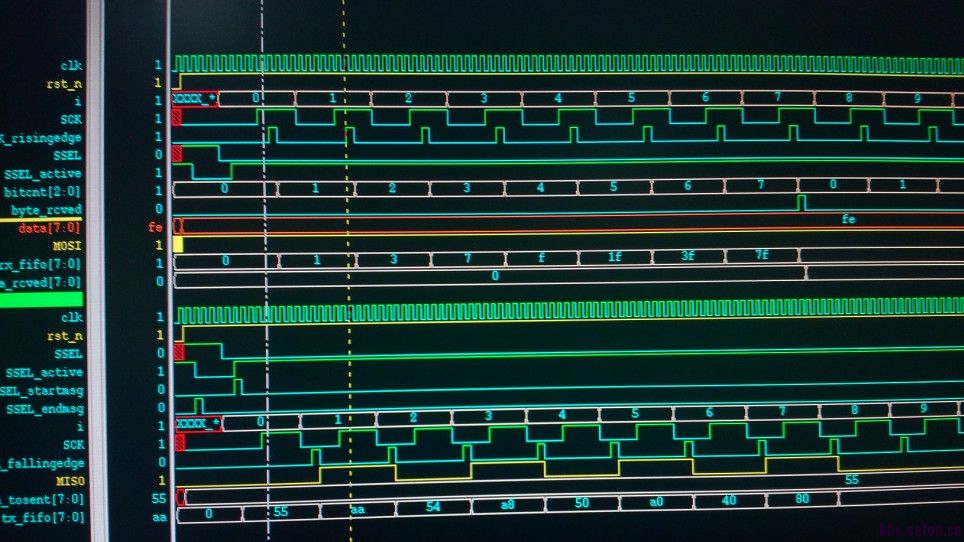

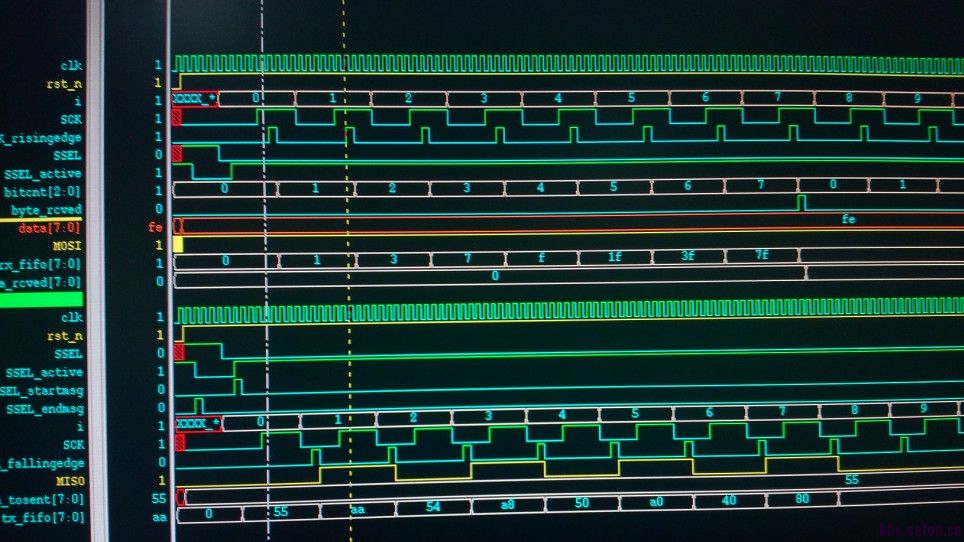

这是send data的波形图,是对的,各位可以比较

(上面一半是rx,是错的;下面一半是tx,是对的)

(上面一半是rx,是错的;下面一半是tx,是对的)

小弟反复研究还是没有发现关键问题所在,望各位大虾帮忙看看,在线等,急!

,写的比较简单,用一个2位的移位寄存器存放MOSI,然后在SCK上升沿把MOSI的高位顺次移位给到rx_fifo[7:0]的低位,当1个字节传完,byte_rcved标志位使能,把rx_fifo中数据输出给byte_data_rcved,完成一次receive data操作。

,写的比较简单,用一个2位的移位寄存器存放MOSI,然后在SCK上升沿把MOSI的高位顺次移位给到rx_fifo[7:0]的低位,当1个字节传完,byte_rcved标志位使能,把rx_fifo中数据输出给byte_data_rcved,完成一次receive data操作。这个是testbench,

下面的问题就比较蛋疼了,看这张receive dat5a的波形图,

。如tb中,MOSI的输入数据 data[7:0] 赋值为35h,但显示到波形就变成了6Ah(也就是data[7:0]左移一位后的数值),反复试验多次都是这个问题(比如输入FF,显示为FE;输入55,显示为AA;输入77,显示为EE)。反复查看过模块代码和tb代码,还是没有头绪,蛋疼!然后MOSI信号线上输出的数据也不对(对的话应该是data[7]的从高位开始顺次输出),rx_fifo和byte_data_rcved的值也是时对时不对。

。如tb中,MOSI的输入数据 data[7:0] 赋值为35h,但显示到波形就变成了6Ah(也就是data[7:0]左移一位后的数值),反复试验多次都是这个问题(比如输入FF,显示为FE;输入55,显示为AA;输入77,显示为EE)。反复查看过模块代码和tb代码,还是没有头绪,蛋疼!然后MOSI信号线上输出的数据也不对(对的话应该是data[7]的从高位开始顺次输出),rx_fifo和byte_data_rcved的值也是时对时不对。这是send data的波形图,是对的,各位可以比较

(上面一半是rx,是错的;下面一半是tx,是对的)

(上面一半是rx,是错的;下面一半是tx,是对的)小弟反复研究还是没有发现关键问题所在,望各位大虾帮忙看看,在线等,急!

这是因为SCK有unknown状态,从unknown到0被仿真器识别成了一个negedge,data被左移了一位

但MOSI的时候,是在posedge,有关系吗?而且如果像您说的,那MISO岂不也要受到影响?

2楼说的没错,tb中SCK提前翻转一次。

你的代码里面有些写法不合适,可综合模块中,一个寄存器不好在两个always赋值的;

即使是在tb中的always 时序逻辑,也避免用‘=’赋值。

谢谢兄弟,确实是这个问题。另外就是$finish语句写在了always里面,所以只移位了一次,重写了一个initial,现在波形对了。

谢谢兄弟,确实是这个问题。另外就是$finish语句写在了always里面,所以只移位了一次,重写了一个initial,现在波形对了。

最近也在学习SPI slave,是否可以给发一个slave的代码,万分感谢。

827597077@qq.com

小编 你好!我也是在学习SPI这块,却是一头雾水,不知道该怎么学习,能否把你的经验传授下。