关于DDR2的IP核仿真问题,求助!

时间:10-02

整理:3721RD

点击:

最近刚做DDR2,周围也没个人指导,效率特别低还各种弄不懂,希望热心的大神们多多帮助,跪谢!

开发环境

ISE 14.3

MIG 3.6

FPGA vc4vsx55 DDR2 MT47H32M16xx-3

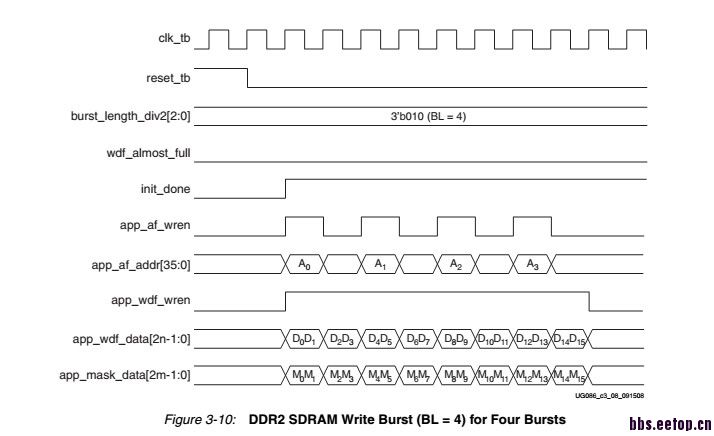

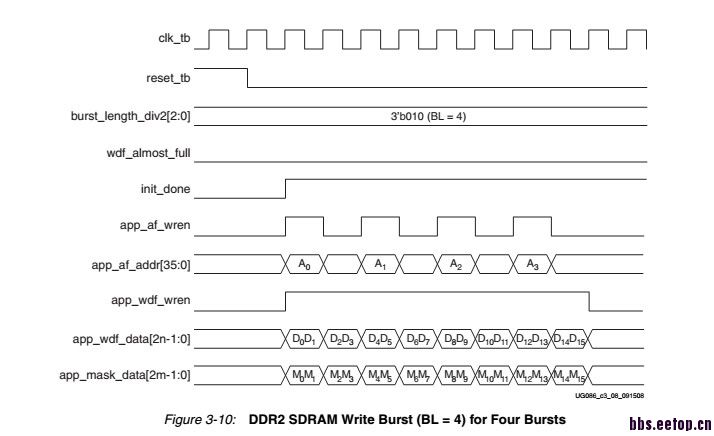

根据ug086中指导,建完核之后按figure3-10的时序图写了一段简单实现写操作的代码,其中只对时序图中的信号进行了操作,其它只是简单定义了一下,用ISE自带的Isim对user guide中的sim进行仿真【不知为何,将ddr2_model.v放到modelsim中编译时会有很多类似xxlength未定义的错误所以后来选择了Isim】,结果在200us左右时仿真停止,显示ERROR: Activate Failure. Initialization sequence is not complete.并且ini_done也一直未拉高,实在弄不懂怎么回事啊,希望做过DDR2的大神们指点一下,不胜感激!

开发环境

ISE 14.3

MIG 3.6

FPGA vc4vsx55 DDR2 MT47H32M16xx-3

根据ug086中指导,建完核之后按figure3-10的时序图写了一段简单实现写操作的代码,其中只对时序图中的信号进行了操作,其它只是简单定义了一下,用ISE自带的Isim对user guide中的sim进行仿真【不知为何,将ddr2_model.v放到modelsim中编译时会有很多类似xxlength未定义的错误所以后来选择了Isim】,结果在200us左右时仿真停止,显示ERROR: Activate Failure. Initialization sequence is not complete.并且ini_done也一直未拉高,实在弄不懂怎么回事啊,希望做过DDR2的大神们指点一下,不胜感激!

你的写程序贴出来看一下i