跪求指导modelsim仿真lpm_rom高阻。

modelsim 仿真 lpm_rom...........................

我只是想看下 我的rom初始化 是不是成功 。在网上 借鉴了很多人的 步骤。

我自己的操作的步骤如下:已经 修改了

Veriuser = \<dll directory>\convert_hex2ver.dll

首先,quartus 建立工程:新建hex文件(rom位宽为8,深度为16)->

输入值保存->

用megawizard 生成单口rom,其中关联了hex文件,生成了rom.v,rom_bb.v文件->

在 modelsim中 生成库,库中包含了 altera_mf.v和220model.v 两个文件

再新建 work,添加rom.v, rom_bb.v, test.v三个文件,编译,仿真并且libraries 中添加了我自己生成的 库 。。我就是这么一步一步来的。为什么为什么 波形 读出的rom的值就是高阻呢?高手 们 快点来给我帮帮忙啦 。女生搞工程 ,真的是伤不起。简单的仿真都做不好。愁苦

¥¥¥¥¥¥¥¥¥¥¥¥¥

我怀疑 是不是 我的 rom 初始化文件没有 弄好。是不是 在生成rom的过程中关联了 .hex文件,生成的rom.v文件里就有了 rom的初始值,在 modelsim仿真的时候 工程里加了可以 包含初始值的rom.v ,

可是我打开rom.v ,没有看到初始值写在哪里了的啊。。这个地方 求解释

¥¥¥¥¥¥¥¥¥¥¥¥¥

testbench是这样的:

module test;

reg clk;

reg [3:0]addr;

wire [7:0]data;

initial

begin

clk=1;

addr=4'b0000;

#520 addr=4'b0001;

#530 addr=4'b0010;

#540 addr=4'b0011;

#550 addr=4'b0100;

#560 addr=4'b0101;

#570 addr=4'b0110;

#580 addr=4'b0111;

#500 addr=4'b1000;

#510 addr=4'b1001;

#500 addr=4'b1010;

end

always #50 clk=~clk;

rom u1(.clock(clk),.address(addr),.q(data));

endmodule

我自己定个先。明天继续来实验室苦逼。简单的工程步骤都搞不好 。两天了 。烦躁不已

测试文件是否正常,可以把测试文件贴出来看下否?

在modelsim中:

看波形,接到IP上的时钟、输入是否正常;

调memmery,看rom里面值是否是正确。

测试文件还蛮简单,因为就是一个8位,深度16的rom。

module test;

reg clk;

reg [3:0]addr;

wire [7:0]data;

initial

begin

clk=1;

addr=4'b0000;

#520 addr=4'b0001;

#530 addr=4'b0010;

#540 addr=4'b0011;

#550 addr=4'b0100;

#560 addr=4'b0101;

#570 addr=4'b0110;

#580 addr=4'b0111;

#500 addr=4'b1000;

#510 addr=4'b1001;

#500 addr=4'b1010;

end

always #50 clk=~clk;

rom u1(.clock(clk),.address(addr),.q(data));

endmodule

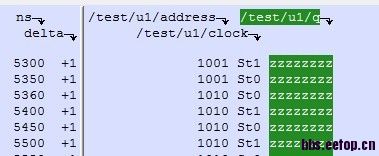

仿真波形,clk 和address 的值都是正确的,跟测试文件写的一样。只是输出data不一样。请问怎样调用memory呢

quartus rom的初始文件是.hex?我怎么记得貌似是.mif的。

两种文件 ,但是因为 modelsim 只能识别 .hex文件,所以不用.mif文件的。楼上还有别的建议吗

view -> memmery list

谢楼上,,,,我看了list ,

# Loading D:\altera\10.1\quartus\eda\mentor\modelsim\convert_hex2ver.dll

# Loading C:\Novas\Debussy\share\PLI\modelsim_pli54\WINNT\novas.dll

# Loading work.test

# Loading work.rom

但是我在网上看到的一个人的 正确的 输出里还有loading altera_mf.v,220model.v,。为什么我也加了库,按照网上的那个 步骤加的 。但是没有 这个loading呢,,,这个会不会就是我的问题所在呢 。。

可能是你的rom没生成好,rom没有完成初始化,你能把rom.v的代码贴出来吗?里面应该有一项初始化文件的参数...可以看这个参数是否指定了对应的初始化文件.

`timescale 1 ns / 1 ns

// synopsys translate_on

module rom (

address,

clock,

q);

input [3:0] address;

input clock;

output [7:0] q;

`ifndef ALTERA_RESERVED_QIS

// synopsys translate_off

`endif

tri1 clock;

`ifndef ALTERA_RESERVED_QIS

// synopsys translate_on

`endif

wire [7:0] sub_wire0;

wire [7:0] q = sub_wire0[7:0];

altsyncram altsyncram_component (

.address_a (address),

.clock0 (clock),

.q_a (sub_wire0),

.aclr0 (1'b0),

.aclr1 (1'b0),

.address_b (1'b1),

.addressstall_a (1'b0),

.addressstall_b (1'b0),

.byteena_a (1'b1),

.byteena_b (1'b1),

.clock1 (1'b1),

.clocken0 (1'b1),

.clocken1 (1'b1),

.clocken2 (1'b1),

.clocken3 (1'b1),

.data_a ({8{1'b1}}),

.data_b (1'b1),

.eccstatus (),

.q_b (),

.rden_a (1'b1),

.rden_b (1'b1),

.wren_a (1'b0),

.wren_b (1'b0));

defparam

altsyncram_component.clock_enable_input_a = "BYPASS",

altsyncram_component.clock_enable_output_a = "BYPASS",

`ifdef NO_PLI

altsyncram_component.init_file = "rom.rif"

`else

altsyncram_component.init_file = "rom.hex"

`endif

,

altsyncram_component.intended_device_family = "Cyclone II",

altsyncram_component.lpm_hint = "ENABLE_RUNTIME_MOD=NO",

altsyncram_component.lpm_type = "altsyncram",

altsyncram_component.numwords_a = 16,

altsyncram_component.operation_mode = "ROM",

altsyncram_component.outdata_aclr_a = "NONE",

altsyncram_component.outdata_reg_a = "CLOCK0",

altsyncram_component.widthad_a = 4,

altsyncram_component.width_a = 8,

altsyncram_component.width_byteena_a = 1;

endmodule

以上是我在quartus 生成的 rom.v,我 看到其中是关联 了 rom.hex文件的 。

将altsyncram_component.init_file = "rom.hex"中的rom.hex换成全路径的,例如

altsyncram_component.init_file = "c:/xx/rom.hex"注意用左斜杠

继续坐等 高手指点。一点点问题搞不定了

非常谢谢楼上的 多次 回答。好人呐.我先试试 这个 方法行不行

可是楼上的好好先生,还是不行,。高阻高阻!

看看是不是这个 http://blog.csdn.net/zd_2010/article/details/41864167

姐姐,我也遇到了同样的问题啊,modelsim 总是出现高阻阿?你有没有解决阿!