什么是源同步接口?(图)

时间:10-02

整理:3721RD

点击:

,图中,左侧两个寄存器中没有DATA1和DATA2啊

,图中,左侧两个寄存器中没有DATA1和DATA2啊

Data信号是多bit的,时序图中的DATA1和DATA2表示Data中的两个bit

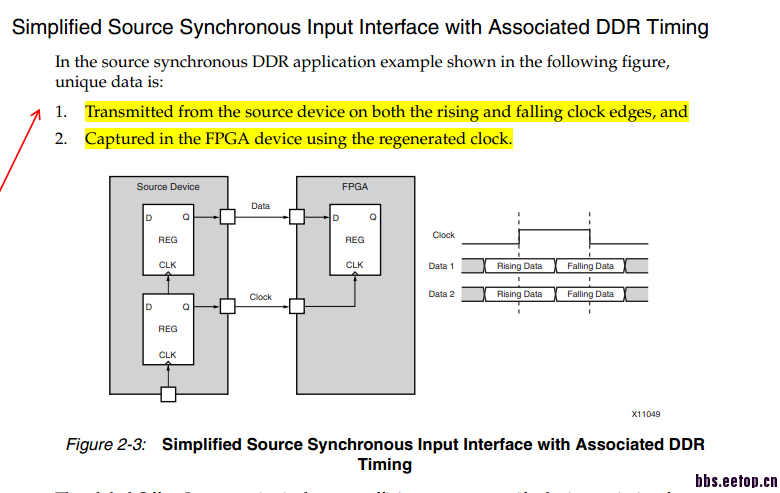

源同步就是上游设备发送数据的的同时还发送时钟,且数据和时钟保持一定的相位关系,如相位对齐,那么下游数据就使用这个时钟才采样输入的数据。这就叫源同步

与之相应的是系统同步,就是一个外部时钟源同时给上下游两个设备供给时钟,上游设备用这个时钟发数据,下游设备用这个时钟采数据。

你看的应该是Xilinx的 timing closure,仔细看看图就能知道源同步和系统同步的区别

也正在做一个系统,都是视频的60P的输入数据,而且多路。即148.5M随路时钟信号多路进来,fpga再给打到后端的多路dsp接收。为了减少时钟,采用主时钟50M通过dcm产生一个148.5M的时钟,来统一输出的时钟。之间用fifo隔离,现在的问题是,如何保证输出的148.5M跟fifo读出的data输出时满足需要的相位关系?能设置offsetout吗?用的是可怜的spartan3a。哪位高手解释下,谢谢。可以发到cfddesign@qq.com。谢谢。

fifo读时钟和读的数据之间的相位关系应该是固定的吧