FPGA通过CPU引导启动

Spartan6有个讲config的手册,上面应该有时序图。

FPGA 配置为 serial slave 的模式,CPU加载FPGA的bin文件,xilinx最近刚刚推出一个xapp1188

我找到了部分资料,分享下:

http://wenku.baidu.com/link?url=XsxADROiohFIXYsITgyE-b5yq31Cvxrr7Py-S4GAbQs79yFTcxXA--WBFgi3AO6qFLE93qo8riM_VGUqyDIZE8mc4Nx643289ju4rAg22LG

http://wenku.baidu.com/link?url=9jIbpQxgUvhdEozFdTtdmMe0_RiaQxoja8zo808zrGWUtVlPQ3hXuWp_IzuY0WK4oFQbYun2IlyBSNanowEMZIeqq6lqmkx9tCXaLcrzHsq

现在已经实现功能,代码如下

char FPGA_LoadCode_INIT(void)

{

int i;

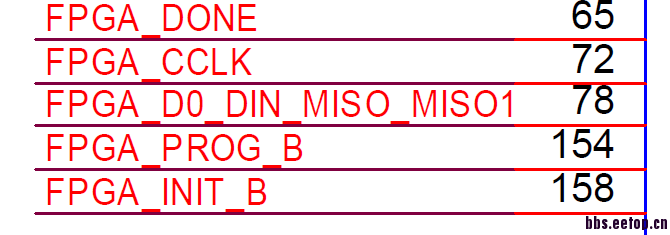

//引脚初始化

FPGADONEINIT;

FPGACCLKINIT;

FPGADININIT;

FPGAPROGINIT;

FPGAINITINIT;

CCLK_H;

PROG_H;

//清空FPGA内存数据

i=200;

while(1)

{

if(READINIT==1)

{

break;

}

i--;

if(i==0)

{

return 1;

}

}

CCLK_L;

PROG_L;

i=20;

while(i--);

PROG_H;

i=65000;

while(1)

{

if(READINIT==1)

{

break;

}

i--;

if(i==0)

{

return 2;

}

}

return 0;

}

char FPGA_LoadCode_Updata(UINT8* idata,UINT32 idatalen)

{

char ret;

UINT32 i;

for(i=0;i<idatalen;i++)

{

FPGA_UpdataOneByte(idata);

}

if(READINIT==0)

{

return 1;

}

return 0;

}

void FPGA_UpdataOneByte(UINT8 idata)

{

UINT8 cdata=0x80;

UINT8 i=0;

for(i=0;i<8;i++)

{

CCLK_L;

if(idata&cdata)

{

DIN_H;

}

else

{

DIN_L;

}

cdata>>1;

CCLK_H;

}

CCLK_L;

}