请求大神指导啊 !

时间:10-02

整理:3721RD

点击:

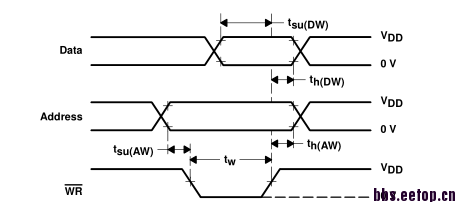

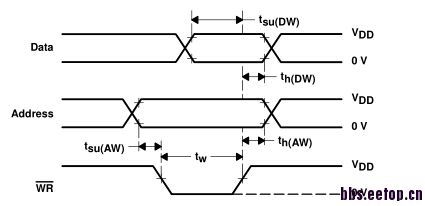

我现在是用FPGA控制DAC输出双极性的锯齿波 DAC的时序图是这样

我现在是用FPGA控制DAC输出双极性的锯齿波 DAC的时序图是这样 [img]file:///C:\Program Files\Tencent\QQ\Users\815090504\Image\C2C\CV`ZYRU%OBOPOOAT5[)$C3P.png[/img][img]file:///C:\Program Files\Tencent\QQ\Users\815090504\Image\C2C\CV`ZYRU%OBOPOOAT5[)$C3P.png[/img]

[img]file:///C:\Program Files\Tencent\QQ\Users\815090504\Image\C2C\CV`ZYRU%OBOPOOAT5[)$C3P.png[/img][img]file:///C:\Program Files\Tencent\QQ\Users\815090504\Image\C2C\CV`ZYRU%OBOPOOAT5[)$C3P.png[/img]

那DAC延时时序代码要怎么写呢?

试试:

使用一个时钟信号,要求周期T大于任何一个时序要求,即(T>Tsu) & (T>Th) & (T>Tw)

使用时钟驱动产生DAC接口信号。

因为你的数据一定是时钟驱动的,所以....

好的 我试试 谢谢哈

我时序可不可以这样写呢?

这里的时序我分为add2拉低、WR拉低和赋值、WR拉高、add2拉高4个阶段。

always@(posedge adc_clk or negedge rst_n)

begin

if(!rst_n)

begin

next<=state1;

add2<=2'b11;

wr<=1'b1;

end

else

case(next)

state1:

begin

add2<=2'b00;

next<=state2;

end

state2:

begin

wr<=1'b0;

data_dac<=cout;

next<=state3;

end

state3:

begin

wr<=1'b1;

next<=state4;

end

state4:

begin

add2<=2'b00;

next<=state4;

end

endcase

end

其中adc_clk周期为0.02s