面试小考题, 有图有真相!

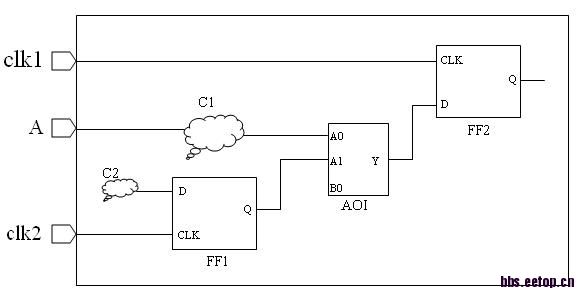

如上图所示,请问 A->FF2 是否需要检查timing,如果需要的话,请计算 A->FF2 的setup是否满足,slack=? 已知条件如下:

create_clock clk1 -period 10n

create_clock clk2 -period 40n

set_clock_uncertainty -setup 50p clk1

set_clock_uncertainty -setup 200p clk2

set_false_path -hold -from clk1 to clk2

set_false_path -hold -from clk2 to clk1

set_input_delay -clock clk2 1n A

library setup (FF1/FF2) = 150p

AOI delay = 0.5n

C1 delay = 8.5n

C2 delay = 5n

clkb是不是应该设input_delay啊,而不设clock source latency啊?

嗯, clkb本身是clock, 约束和一般clock一样比如uncertainty

顶一下

小编,你面试的是IC还是FPGA啊? 要是FPGA的面试题是这样,有些难度了

50P不知道对不

A相对于clk1没有input_delay的话,slack是0.8ns吧。

跟着你们学习

学习 马上也要找工作了

A和FF2之间有通路PATH,要检查timing

FF1和FF2之间的通路不需要检查timing,因为异步时钟

小编改题了啊,之前那个clkb作为data输入的问题怎么处理的啊?

A->FF2的setup需要检查的吧,由于A的input delay没有用clk1约束,按照0来计算的话是不是应该slack=-1ns,不满足啊?

A->FF2需要检查timing

1.如果没有input daley ,即clk1好A是对其的。

slack=period 10ns-AOI delay 0.5ns -C1 delay 8.5ns -50ps=950ps

呵呵, 似乎和主考官的答案相距甚远啊

提示: 两个uncertainty的约束不是打酱油的。

如上图所示,请问 A->FF2 是否需要检查timing,如果需要的话,请计算 A->FF2 的setup是否满足,slack=? 已知条件如下:

create_clock clk1 -period 10n

create_clock clk2 -period 40n

set_clock_uncertainty -setup 50p clk1

set_clock_uncertainty -setup 200p clk2

set_false_path -hold -from clk1 to clk2

set_false_path -hold -from clk2 to clk1

set_input_delay -clock clk2 1n A

library setup (FF1/FF2) = 150p

AOI delay = 0.5n

C1 delay = 8.5n

C2 delay = 5n

一点一点说

1.clk1 10ns 周期

2.clk2 40ns周期

3.50p skew clk1

4.200p skew clk2

5.不关心

6.不关心

7.后边写的A不知道啥意思 前边clk2输入延迟1ns

8.FF1 FF2 setup 150ps

由于只考虑 A-FF2 的路径只用考虑 CLK1时钟域

那么 slack=时钟周期+skew - daley-FF2_setup=10ns +50ps-8.5ns-0.5ns-150ps=900ps

我个人认为clk1 和A的关系都没说清楚......

不算clk1 input delay

slack=10-0.05-8.5-0.5-0.15=0.8ns

需要检查

slack = -0.15ns

set_input_delay -clock clk2 1n A

这个意思是不是说 A落后于CLK2 1ns呢?

我觉得slack是0.8ns

当A1一直保持一个电平的时候 slack = 10 - 8.5 -0.5 -150ps-50ps = 0.8 ns

当A1变化的时候,因为A1的稳定要提前于A0,

所以slack还是不变化的

这时我的理解

1.因为clk1和clk2没有设置false path,则需要检查他们之间的timing,虽然两个时钟是异步的,但是软件默认clk1和clk2的第一个上升沿是对齐的。

2. 因为设置了input delay,即假设到达A端口的数据是由clk2产生的:clk2的上升沿打出A端口的数据,到达A端口耗时1ns. 这个数据继续向内传播耗时8.5ns到达IOA,又经过0.5ns到达FF2的D端口。总耗时1+8.5+0.5=10ns. 即FF2的D端口的数据是由clk2打出来的,经过10ns传播到FF2的D端口。

3. 由以上的1和2,得出结论,如果不考虑uncertainty,则timign slack 是 -0.15ns.即:由于clk1的周期是10ns,setup time是0.15ns, 而D端口的数据在第一个上升沿打出后(其实是clk2打出的D端口的数据,但是有一上面所述的第1点,软件认为两个clk的第一个上升沿是同时的), 经过10ns到达D端口, 所以slack= -0.15ns.

4. 因为设置了两个clk的uncertainty,则软件自动按照最严格的情况ckeck timing。在这个场景下,最严格的情况是,clk1快0.05ns,clk2 慢0.2ns.于是,slack 变得更糟,-0.15-0.05-0.2=-0.4ns.

请问小编对否?还有题吗,多上几道题,也让我等开心开心

setup slack=data required time - data arrival time

data required time=latch edge + latch clock delay - utsu

data arrival time=launch edge + launch clock delay + input delay + pin to register delay

此题中launch clock是clk2,latch clock是clk1,因此data required time和data arrival time分别可计算得到:

data required time=10ns - 0.05ns - 0.15ns=9.8ns

data arrival time=0ns + 0.2ns + 1ns + (8.5ns + 0.5ns)=10.2ns

因此得到A-FF2对应的setup slack=9.8ns - 10.2ns= -0.4ns,不满足

AT = 1ns + 8.5ns + 0.5ns = 10ns

RT = 10ns - 0.05ns - 0.15ns = 9.8ns

Slack = RT - AT = -0.2ns

学习一下,谢谢了

,呵呵,我算错了,算成了0.8了,你有这方面的实例吗?

这个需要看DC的workshop就可以了

分析一下

看不懂先学习着

AOI是什么呀?

麻烦问下 这个图里的AIO是什么东东?

(10-0.15-0.05)-(8.5+0.5)=0.8ns

顶一下