关于一个移位操作电路的实现

时间:10-02

整理:3721RD

点击:

入门菜鸟求大神们指教

1:现在想得到这样一个移位操作的电路(4bit输出):输出初始状态要求是0001,为时钟上升沿触发,后面每来一个上升沿,输出变化为0010,0100,1000,0001,0010,0100.......时钟低电平时,保持当前状态。本人对verilog不懂,请教怎么写RTL。

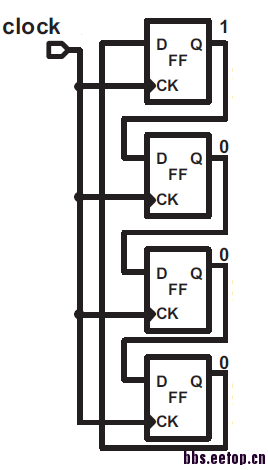

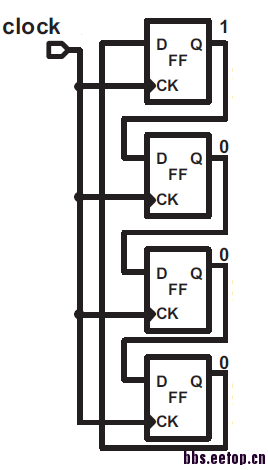

2:我也找到一个电路,可以实现上述功能(见图),在这样的电路图中,怎样才能使初始状态是0001呢?好像不能直接给最上面的寄存器高电平呀

1:现在想得到这样一个移位操作的电路(4bit输出):输出初始状态要求是0001,为时钟上升沿触发,后面每来一个上升沿,输出变化为0010,0100,1000,0001,0010,0100.......时钟低电平时,保持当前状态。本人对verilog不懂,请教怎么写RTL。

2:我也找到一个电路,可以实现上述功能(见图),在这样的电路图中,怎样才能使初始状态是0001呢?好像不能直接给最上面的寄存器高电平呀

就这个电路可以,初始的1靠置位端,其他三个是复位端。

{ff_reg3,ff_reg2,ff_reg1,ff_reg0} <= {ff_reg2,ff_reg1,ff_reg0,ff_reg3};

May be you can try it. The example shows below.

Your diagram dosen't shows rest signal therefore the register can't be set an initial value.

I hope that can help you.

Example:

reg [3:0] data_reg;

always @(posedge CLK or negedge RSTn_)

if(~RSTn_)

data_reg <= 4'b0001;

else

data_reg <= data_reg << 1;

always @(posedge CLK or negedge RSTn_)

if(~RSTn_)

data_reg <= 4'b0001;

else

data_reg <= data_reg << 1;

学习下。

always @ (posedge clk or negedge rst)

begin

if (!rst) begin

Q <= 4'b0001;

end

else begin

Q <= {Q[2:0], Q[3]};

end

end

不少大侠误人子弟来了

6楼正解