小白求助,一个电路问题

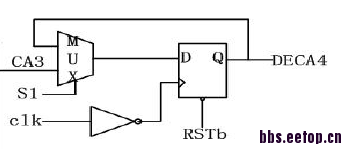

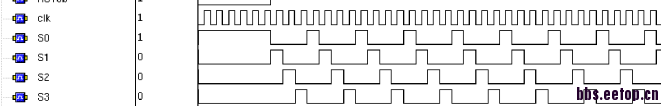

如图所示,一篇硕士论文里的一个图,图的意思是在是在s1节拍选择CA3,并在S1的节拍末写入寄存器中,因为clk下降沿与s1重合(右图所示),所以图中是clk下降沿触发,但这样以来clk下降沿触发,那s1也变成了0,选择器选择的是寄存器本身的值,也就是CA3永远写不进去啊!

大家指导一下呀!

哪有对得刚刚好的,如果不是异步的,一个信号宽度是一个周期,满足时序就会被采样到。

S1是在节拍信号发生器根据clk产生的四个节拍之一,就是一个clk周期,是同步逻辑,那我怎么才能在S1节拍末把在S1节拍产生的信号写入寄存器呢

这样就可以啊。时钟沿先来,然后才是数据变化,仿真的时候加个#1,有利于新人理解。

那这样建立时间成立,但保持时间不一定成立呀!怎么办呢

低速情况下这些时序都不是你要考虑的问题,工具会帮你搞定,所以你自己做功能仿真OK就行了。

对对!谢谢指导!

可否用S1代替CLK?

不行,这个电路就靠s1比clk延迟的那么一点点时间

我在写顶层模块的时候,声明了一个wire型的数据总线DB, 子模块1满足某条件下输出DB1,不满足是高阻态,子模块2里满足某条件输出DB2,不满足是高阻态,两个模块往总线上写数据的时间也不冲突,例化时模块1是.DB1(DB),模块2是.DB2(DB),仿真时DB1却一直是不定态,DB2却一直是高阻态,如果我写成.DB1(DB1),在顶层模块声明一个DB1线,DB1的输出就正确了,但这个线不是我要的总线,求大神指导!

模块1中是这样的吗?

reg DB1_reg;

wire DB1 = 条件 ? DB1_reg : 1'bz;

模块2中是这样的吗?

reg DB2_reg;

wire DB2 = 条件 ? DB2_reg : 1'bz;

第一个问题,时序是什么都没理解,最最简单的同步逻辑。

第二个问题,线与了。

顶一下。

这不就是带使能的D触发器么?S就是使能信号。

今天做代码覆盖率的时候用6.2b做是对的,但用6.1c做加入代码覆盖率后编译出现了两个表达覆盖unsupported infix oprator 和一个条件覆盖unsupported variable type,并且导致功能仿真也错了,求助!

今天做代码覆盖率的时候用6.2b做是对的,但用6.1c做加入代码覆盖率后编译出现了两个表达覆盖unsupported infix oprator 和一个条件覆盖unsupported variable type,并且导致功能仿真也错了,求助!