xilinx RAM使用时,地址比数据慢一拍

时间:10-02

整理:3721RD

点击:

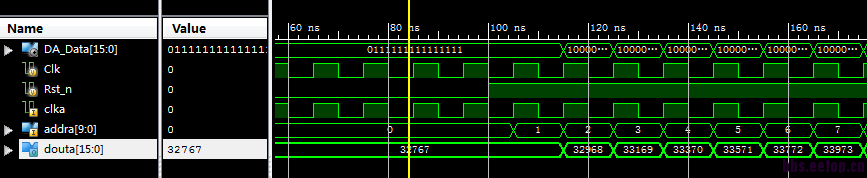

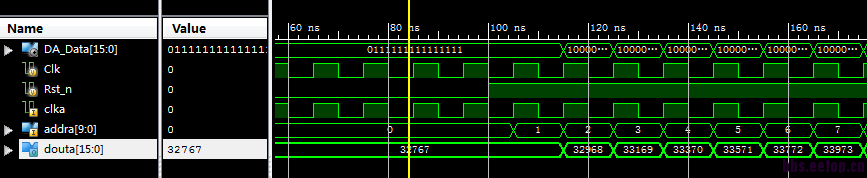

初学者,在仿真xilinx的rom时候,[img]file:///C:\Users\Administrator\AppData\Roaming\Tencent\Users\859757081\QQ\WinTemp\RichOle\7LF%KY4)Q_{VT61[D(M`A49.png[/img]数据总是比地址慢一拍输出,请问这个是创建rom时哪里需要设置吗?

正常。

正常情况下,数据和地址不是应该对齐的吗?

写的时候写数据、写地址、写使能应对齐;但是读的时候,在你给出读使能和读地址之后要有一到两个时钟周期的延迟数据才能出来。不可能你一给地址数据就立即读出来了,站在数字电路的角度考虑那也是不可能的,数字电路都是由门电路实现,门电路都是有延迟的对不对。

恩,明白了,非常感谢

是有延迟的。

写的时候在写使能拉高后的第一个时钟上升沿写入数据,读的时候在读地址改变后的第一个时钟上升沿读出数据

学习。