求助,Chipscope中遇到的奇怪问题

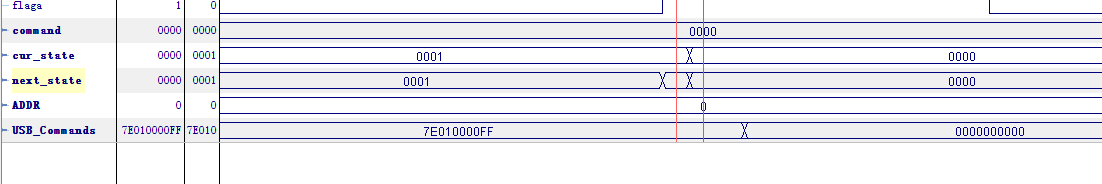

其中状态机我只定义了4个状态;IDLE = 4'b0001,

其中状态机我只定义了4个状态;IDLE = 4'b0001,READ = 4'b0010,

BUSY = 4'b0100,

FINISH = 4'b1000;

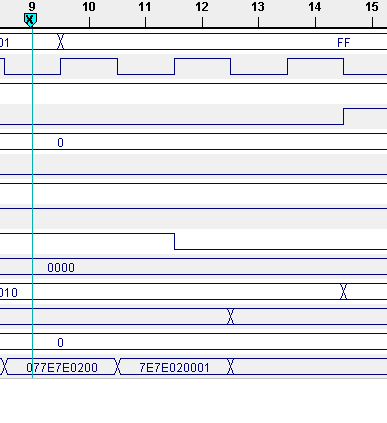

为什么会出现0000的状态呢?

而且next_state和cur_state怎么会同时变成0000呢?不明白是怎么回事?请教大家,如需要我可以把部分代码贴上来。

- always@(posedge clk or negedge rst_n)

- if(!rst_n)

- cur_state<=IDLE;

- else

- cur_state<=next_state;

-

- always@(cur_state,flaga,flagd,ack,USB_Command,empty)

- begin

- next_state = cur_state;

- case(cur_state)

- IDLE:

- begin

- if(flaga == 1'b1)

- next_state = READ_COM;

- end

- READ_COM:

- begin

- if((USB_Command[39:32]==8'h7e)&&(USB_Command[7:0]==8'hff)) //receive

- next_state = BUSY;

- else if(flaga == 1'b0)

- next_state = IDLE;

- end

- BUSY:

- begin

- if((ack == 1'b1)&&(empty==1'b1))

- next_state = FINISH;

- end

- FINISH:

- begin

- if(ack == 1'b0)

- next_state = IDLE;

- end

- endcase

- end

主要看你状态机怎么写的 ,还有就是你用什么时钟抓的

状态机贴出来了,如何是偶尔有抓错的话可能是抓的时钟问题,但这个波形是直接内部逻辑就错了吧?

小编啊,这个情况我遇到过,是你状态机信号第二个always块中有未同步化的异步信号,导致状态机跳飞。

异步信号进来要先过寄存器才行吗?

我知道了,异步信号,使得next_state->cur_state产生了亚稳态,那这个异步信号需要打两拍进来啊?

就是这样,以后设计状态机的时候要记得同步化。

恩 对对 但是latency不就大了啊

同意,状态机输入异步信号必须同步处理,否则一定出现跑飞的情况,一般就是进others里了

屡试不爽

涨姿势了

也遇到这个问题了

LZ啊,不太明白,你的异步信号指的是哪些?你们这个问题的解释感觉没怎么弄懂

异步输入信号,flaga,flagd

这不都是latch么?

哪个是latch?

状态机的if 没有else,不都综合成latch了么?所以会乱跳

有的状态只会跳向另1个状态,不一定是2个。

begin下面有句next_state = cur_state;保证了没有latch吧

谢谢小编 不错的知识

在verilog代码中的状态机的编码并不一定是最终的编码方式,FSM的编码分为好多种 binary gray one-hot等等,最终选择哪一种是工具决定的(如果你没有指明FSM编码方式的话)。

可以在synthysis report 中的low level synthsis中查看实际的FSM编码

谢谢啊。一句话点醒了我,搞了一天的状态机还没发现这个异步信号的问题。