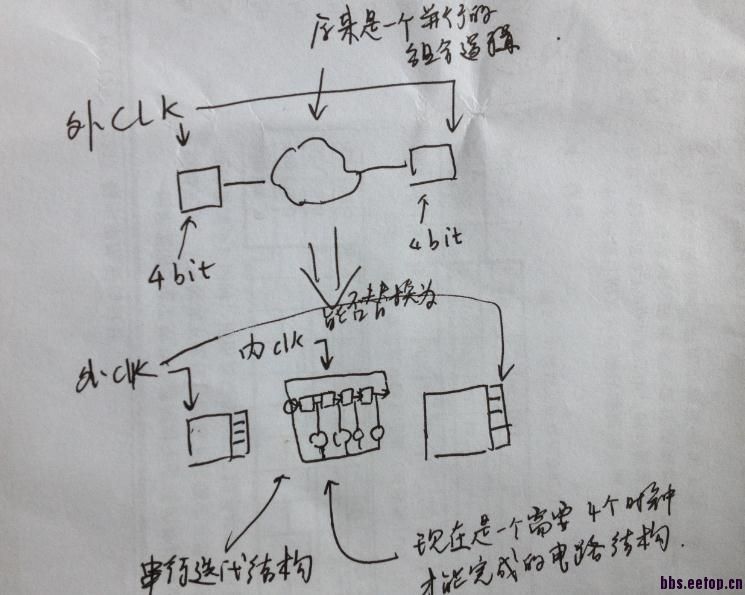

怎么将原有电路中的并行组合逻辑 全部 用 串行迭代时序逻辑 替代掉(有示意图)?

如果外部时钟频率和流水都保持不变的话,没法破

比如现在时钟是100M,这部分组合逻辑路径在一个周期内10ns必须走完,外部时钟和流水不变,里面即使插几级流水,总的路径周期仍然只有10ns,新插入的寄存器还会增加路径延迟,这个无解

只有外部流水也随之增加,比如一个周期出数据变为两个周期才出数据,里面的逻辑才能得到更松的时序约束

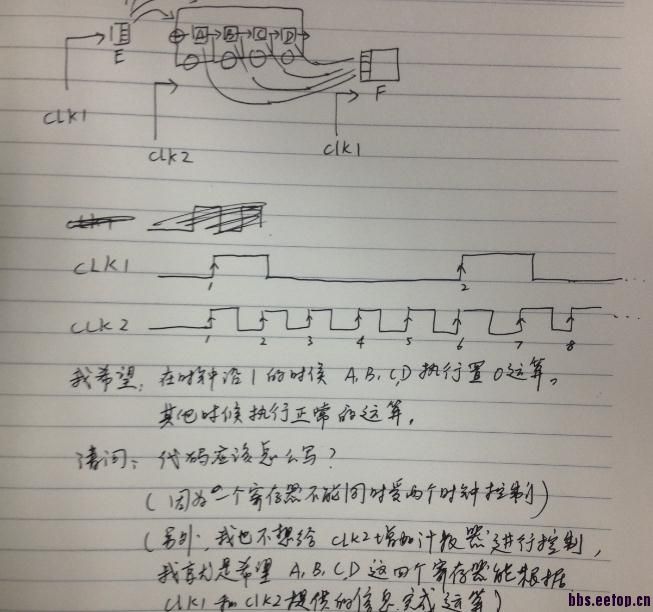

再请教一个问题啊,是不是说控制寄存器的时钟只能有一个?比如有段代码是这样的:

always@(posedge A, posedge B)begin

.....

.......

......

end

是不是说,随后综合的结果中,要么A是时钟信号,要么B是时钟信号,(另外一个信号接到寄存器的使能或者置位/复位端?)

刚才遇到一个很严重的问题(对我来说),具体的我写在纸上了。

综合一个寄存器只有一个时钟沿触发,另一个可用作复位/置位,以此实现清零

外部时钟频率流水都不变的情况下,不知道你这样改的意义何在,中间逻辑的时序约束会更紧

我主要是为了节省资源

请问,还是看上面那张图,我的clk1和clk2是异步的(clk1由clk2分频产生),结果我在做功能仿真的时候,仿真器认为我先运算了时钟沿2(控制内部电路),然后再执行了时钟沿6(控制外部电路)。但是实际上我希望的是,时钟沿2和时钟沿6是完全对齐的。额,你懂我的意思吗,就是时钟沿2(控制外部大的那个寄存器,将内部的几个小寄存器的值打入)和时钟沿6(内部几个小寄存器之间循环流动)是同时进行的,而不是先后进行的。(但是仿真器总是认为,这两个时钟信号是异步的,并且总是有clk2在clk1之后执行)。

怎么解决这个问题呢?可以掉用PLL 或者 XILINX的时钟资源(类似原语,记得好像有BUF之类的东西) 来让这两个异步时钟完全同步吗?