verilog仿真中是有task求助

时间:10-02

整理:3721RD

点击:

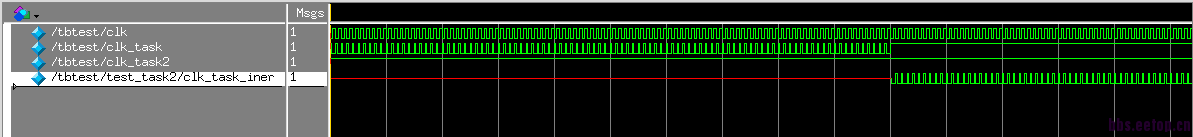

仿真中有些重复的操作考虑用task实现,做了个小的测试如下:

module tbtest();

parameter delay = 10;

reg clk;

reg clk_task;

reg clk_task2;

initial

begin

clk = 1'b0;

clk_task = 1'b1;

clk_task2 = 1'b1;

test_task(5);

test_task2(clk_task2,5);

#500 $stop(2);

end

//always @(clk)

//begin

// test_task(5);

// test_task2(5,clk_task2);

//end

always #(delay*1) clk = ~clk;

task test_task;

input integer delay;

begin

repeat(100)

begin

#delay clk_task = 1'b0;

#(delay+10) clk_task = 1'b1;

end

end

endtask

task test_task2;

output clk_task_iner ;

input integer delay;

begin

repeat(100)

begin

#delay clk_task_iner = 1'b0;

#(delay+10) clk_task_iner = 1'b1;

end

end

endtask

endmodule[/code]

task test_task2没有实现功能,将该task中的信号引出来看 是有变化的,但是clk_task2 meiyou bianhua

请各位帮忙看下

task的返回值只在task结束后才返回,内部的变化是反应不出来的

task的返回值只在task结束后才返回,内部的变化是反应不出来的

测试了下 果然是这样的 十分感谢