新手最近做时序约束的一点总结

1、setup不满足

遇到setup不满足,按照quartus 时序约束手册上的方法,check路径上的组合逻辑cell是否过多;检查IC;在设置里打开 各种优化设置,比如使能 physical Synthesis 、registers retiming 等等 ,看手册即可。

2、hold 不满足

原因大概是data arrival time太短同时clock skew太大,我的做法是对data arrival time 进行约束,set_min_delay ,设延时值为正,结果反而使slack更加严重,观察了下waveform ,发现该约束使 latch edge 延后了.根据保持时间检查公式,

Clock Hold Slack = Data Arrival Time – Data Required Time

Data Required Time = Clock Arrival Time+ μtH + Hold Uncertainty

Clock Arrival Time = Latch Edge + ClockNetwork Delay to Destination Register

显然,要使slack增大,latch edge需提前。即,set min delay 需要设置负值。此时时序约束的slack 为正。不知是否正确,望解惑。

3、跨时钟域信号

在进行时序约束时发现如果不对跨时钟信号进行处理会严重影响时序收敛。检测clock time report 时可观察launch edge 与latch edge 是否为同一时钟域。

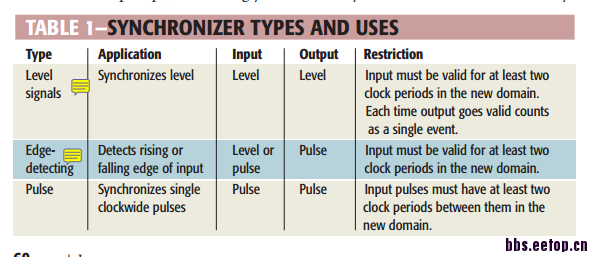

看了篇这方面的经典文章《Crossingthe Abyss——Asynchronous Signals in a Synchronous World》,总结处理方法有

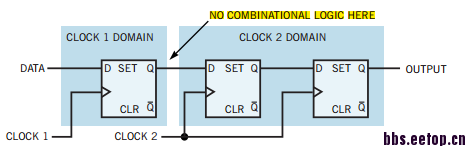

1.慢变化信号,信号变化周期远大于进入时钟域的时钟周期(2-3倍以上),可采用两拍寄存器进行同步,这也是最常用的方法(level )。注意输出也是电平信号,且不论原时钟域的快慢。

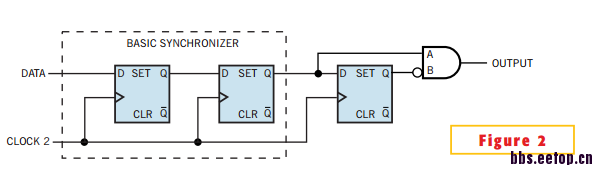

2.边缘检测法,此法与第一种方法类似,区别在于输出端进行了脉冲化处理,故输出为新时钟域的一个周期脉冲。

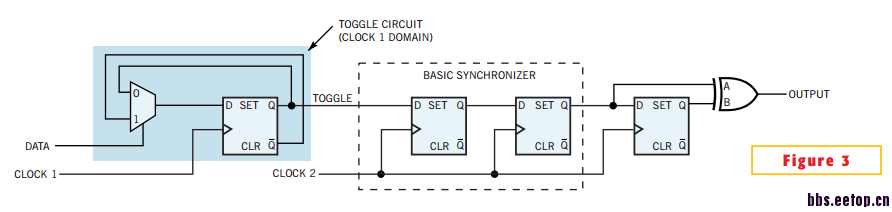

3.脉冲检测法。输入为脉冲信号,且必须仅持续一个原时钟域周期;输出为新时钟域的一个周期脉冲。

同时注意对同步器的第一个reg设置set_false_path,避免错报