求大神相救,感激不尽

library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_arith.all;use ieee.std_logic_unsigned.all; entity lizi1 isport(clk:in std_logic;rst:in std_logic;en:in std_logic;qut std_logic_vector(3 downto 0));end;architecture one of lizi1 issignal q1:std_logic_vector(3 downto 0);beginprocess(clk,en,rst)beginif en='1'thenif rst='1'then q1<="0000";elsif clk'event and clk='1'thenq1<=q1+1;end if;end if;end process;q<=q1;end;

library ieee;use ieee.std_logic_1164.all;entity bcd2 isport(i: in std_logic_vector(3 downto 0);yut std_logic_vector(7 downto 0));end;architecture one of bcd2 isbeginprocess(i)begincase i iswhen"0000"=>y<="11111100";when"0001"=>y<="01100000";when"0010"=>y<="11011010";when"0011"=>y<="11110010";when"0100"=>y<="01100110";when"0101"=>y<="10110110";when"0110"=>y<="10111110";when"0111"=>y<="11100000";when"1000"=>y<="11111110";when"1001"=>y<="11101110";when"1010"=>y<="00111110";when"1011"=>y<="10011100";when"1100"=>y<="01111010";when"1101"=>y<="10011110";when"1110"=>y<="10001110";when"1111"=>y<="11111111";end case;end process;end;

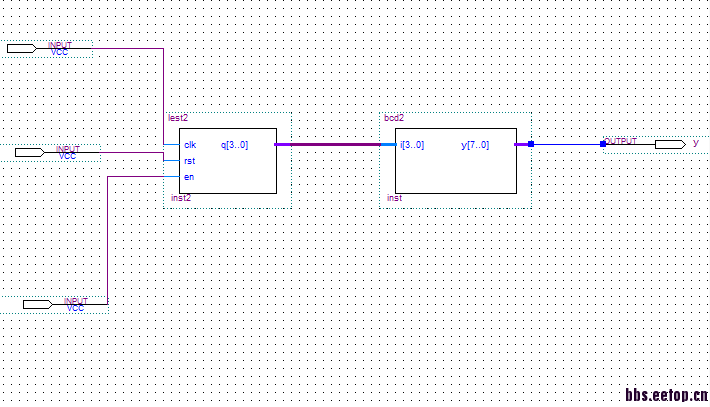

错误如下:Error: Incorrect connector style at port "y[7..0]" for symbol "inst" of type bcd2Error: Can't elaborate top-level user hierarchyError: Quartus II Analysis & Synthesis was unsuccessful. 2 errors, 0 warnings Error: Peak virtual memory: 283 megabytes Error: Processing ended: Sun Nov 23 21:32:01 2014 Error: Elapsed time: 00:00:02 Error: Total CPU time (on all processors): 00:00:01Error: Quartus II Full Compilation was unsuccessful. 4 errors, 0 warnings求大神告知我哪里错了,我改,我改还不行么,

额,代码怎么会这样子,怎么没分段

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_arith.all;

use ieee.std_logic_unsigned.all;

entity lizi is

port(clk:in std_logic;

rst:in std_logic;

en:in std_logic;

qut std_logic_vector(3 downto 0));

end;

architecture one of lizi is

signal q1:std_logic_vector(3 downto 0);

begin

process(clk,en,rst)

begin

if en='1'then

if rst='1'then q1<="0000";

elsif clk'event and clk='1'then

q1<=q1+1;

end if;

end if;

end process;

q<=q1;

end;

library ieee;

use ieee.std_logic_1164.all;

entity bcx is

port(i: in std_logic_vector(3 downto 0);

yut std_logic_vector(7 downto 0));

end;

architecture one of bcx is

begin

process(i)

begin

case i is

when"0000"=>y<="11111100";

when"0001"=>y<="01100000";

when"0010"=>y<="11011010";

when"0011"=>y<="11110010";

when"0100"=>y<="01100110";

when"0101"=>y<="10110110";

when"0110"=>y<="10111110";

when"0111"=>y<="11100000";

when"1000"=>y<="11111110";

when"1001"=>y<="11101110";

when"1010"=>y<="00111110";

when"1011"=>y<="10011100";

when"1100"=>y<="01111010";

when"1101"=>y<="10011110";

when"1110"=>y<="10001110";

when"1111"=>y<="11111111";

end case;

end process;

end;

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_arith.all;

use ieee.std_logic_unsigned.all;

entity lizi is

port(clk:in std_logic;

rst:in std_logic;

en:in std_logic;

qut std_logic_vector(3 downto 0));

end;

architecture one of lizi is

signal q1:std_logic_vector(3 downto 0);

begin

process(clk,en,rst)

begin

if en='1'then

if rst='1'then q1<="0000";

elsif clk'event and clk='1'then

q1<=q1+1;

end if;

end if;

end process;

q<=q1;

end;

library ieee;

use ieee.std_logic_1164.all;

entity bcx is

port(i: in std_logic_vector(3 downto 0);

yut std_logic_vector(7 downto 0));

end;

architecture one of bcx is

begin

process(i)

begin

case i is

when"0000"=>y<="11111100";

when"0001"=>y<="01100000";

when"0010"=>y<="11011010";

when"0011"=>y<="11110010";

when"0100"=>y<="01100110";

when"0101"=>y<="10110110";

when"0110"=>y<="10111110";

when"0111"=>y<="11100000";

when"1000"=>y<="11111110";

when"1001"=>y<="11101110";

when"1010"=>y<="00111110";

when"1011"=>y<="10011100";

when"1100"=>y<="01111010";

when"1101"=>y<="10011110";

when"1110"=>y<="10001110";

when"1111"=>y<="11111111";

end case;

end process;

end;

这不是模块的问题,是你顶层例化的问题。

你检查一下顶层例化和IO管脚。