求助,仿真时候时序自动改变?

时间:10-02

整理:3721RD

点击:

1

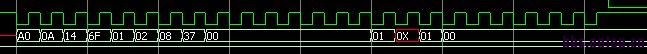

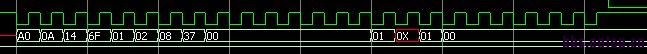

在做一个和dsp通讯的程序,FPGA接收DSP的数据,以下是移位输入的时序图

最上面是输入时钟,

dsp_fsx是帧同步信号,低电平时候数据有效

第三个dsp_rcv是数据有效信号,配合第四个信号使用

第四个是计数,到‘F’的时候,数据有效信号置1

仿真的时候发现前几个数据有效信号dsp_rcv是在帧同步dsp_fsx为高的时候置1,下一帧第二个时钟计数器为1

但是突然自己就变了,下一帧第一个时钟的时候计数器就为1,这是为什么?

2

还有个现象

我在程序预设的一组数据,写fifo的时候其中某个数据仿真出来时0x,实际应该是01

以下是代码

--这是固定数组格式定义

type frontdata2write is array(0 to 24) of std_logic_vector(7 downto 0);

SIGNAL front_data:frontdata2write:=( x"a0",x"0a",

x"14", x"6f", x"01",x"02",

x"08",x"37",

x"00",x"00",x"00",x"00",x"00",x"00",

x"00",x"01",

x"01",

x"01",

x"00",x"00",

x"00",

x"00",x"00",x"00",x"00" );

--以下是循环写数据

..........

elsif rs422_clk6m'event and rs422_clk6m='1' then

case rs422_fifo_wr_state is

when "000" =>

rs422_fifo_wr<='1';

if dsp_ready='1' and rs422_send_ing='0' then

rs422_fifo_wr_state<="001";

end if;

when "001" =>

if pack_front='0' then --固定数组是否发送完毕信号,0表示未发送完毕

n:=0; --n就是计数用的

rs422_fifo_wr_state<="010";

end if;

when "010" =>

rs422_fifo_wr<='0'; --fifo写使能

rs422_fifo_data<=front_data(n); --读取第n个固定数组中的数赋值给fifo输入信号

rs422_fifo_wr_state<="011";

when "011" =>

rs422_fifo_wr<='1';

if n=24 then

rs422_fifo_wr_state<="100";

pack_front<='1'; --固定数组发送完毕,信号置1

n:=0;

else

n:=n+1; --未发送完毕,则计数加1

rs422_fifo_wr_state<="010";

end if;

when "100" =>

. ....

-------------------------

HELP

在做一个和dsp通讯的程序,FPGA接收DSP的数据,以下是移位输入的时序图

最上面是输入时钟,

dsp_fsx是帧同步信号,低电平时候数据有效

第三个dsp_rcv是数据有效信号,配合第四个信号使用

第四个是计数,到‘F’的时候,数据有效信号置1

仿真的时候发现前几个数据有效信号dsp_rcv是在帧同步dsp_fsx为高的时候置1,下一帧第二个时钟计数器为1

但是突然自己就变了,下一帧第一个时钟的时候计数器就为1,这是为什么?

2

还有个现象

我在程序预设的一组数据,写fifo的时候其中某个数据仿真出来时0x,实际应该是01

以下是代码

--这是固定数组格式定义

type frontdata2write is array(0 to 24) of std_logic_vector(7 downto 0);

SIGNAL front_data:frontdata2write:=( x"a0",x"0a",

x"14", x"6f", x"01",x"02",

x"08",x"37",

x"00",x"00",x"00",x"00",x"00",x"00",

x"00",x"01",

x"01",

x"01",

x"00",x"00",

x"00",

x"00",x"00",x"00",x"00" );

--以下是循环写数据

..........

elsif rs422_clk6m'event and rs422_clk6m='1' then

case rs422_fifo_wr_state is

when "000" =>

rs422_fifo_wr<='1';

if dsp_ready='1' and rs422_send_ing='0' then

rs422_fifo_wr_state<="001";

end if;

when "001" =>

if pack_front='0' then --固定数组是否发送完毕信号,0表示未发送完毕

n:=0; --n就是计数用的

rs422_fifo_wr_state<="010";

end if;

when "010" =>

rs422_fifo_wr<='0'; --fifo写使能

rs422_fifo_data<=front_data(n); --读取第n个固定数组中的数赋值给fifo输入信号

rs422_fifo_wr_state<="011";

when "011" =>

rs422_fifo_wr<='1';

if n=24 then

rs422_fifo_wr_state<="100";

pack_front<='1'; --固定数组发送完毕,信号置1

n:=0;

else

n:=n+1; --未发送完毕,则计数加1

rs422_fifo_wr_state<="010";

end if;

when "100" =>

. ....

-------------------------

HELP

补图片= =

我把pack_front信号在case000 里面赋值‘0’之后就正确了。这又是为神马