关于ALTLVDS_TX/RX无法使用相位偏移的问题

时间:10-02

整理:3721RD

点击:

我非常简单的例化了一个LVDS_TX的程序

module LVDS_test (

input clk, // Clock

output [1:0]tx_out,

output TCLk

);

AD9928_SIM_tx LVDS_TX_TEST(

.tx_in (16'hA5_F0),

.tx_inclock (clk),

.tx_out (tx_out),

.tx_outclock(TCLk)

);

endmodule

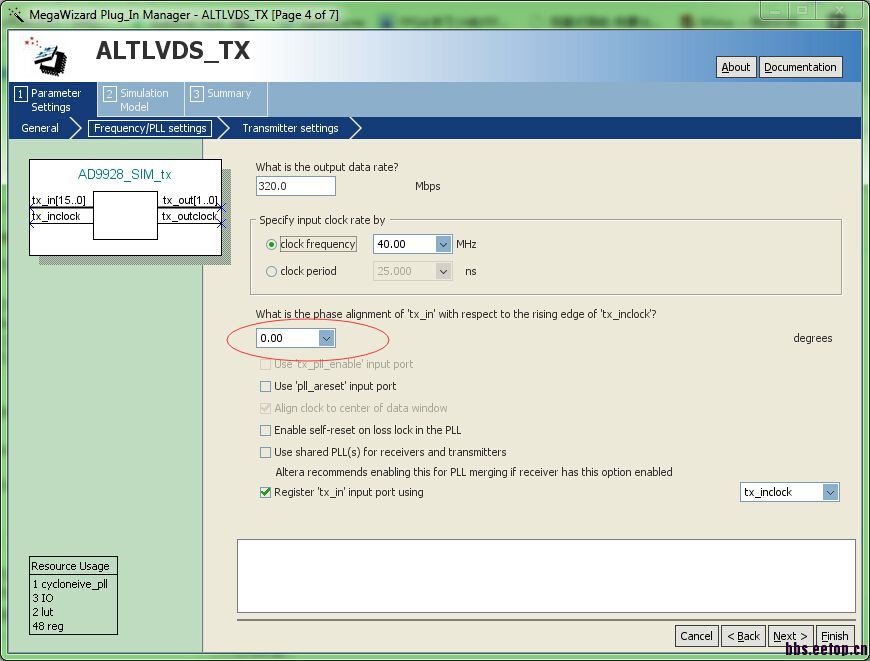

数据用固定的0xA5F0,输入40MHz时钟,输出是两通道,每通道有8个串行因子(2channel*8factor)

输出是320Mbps(如下图)

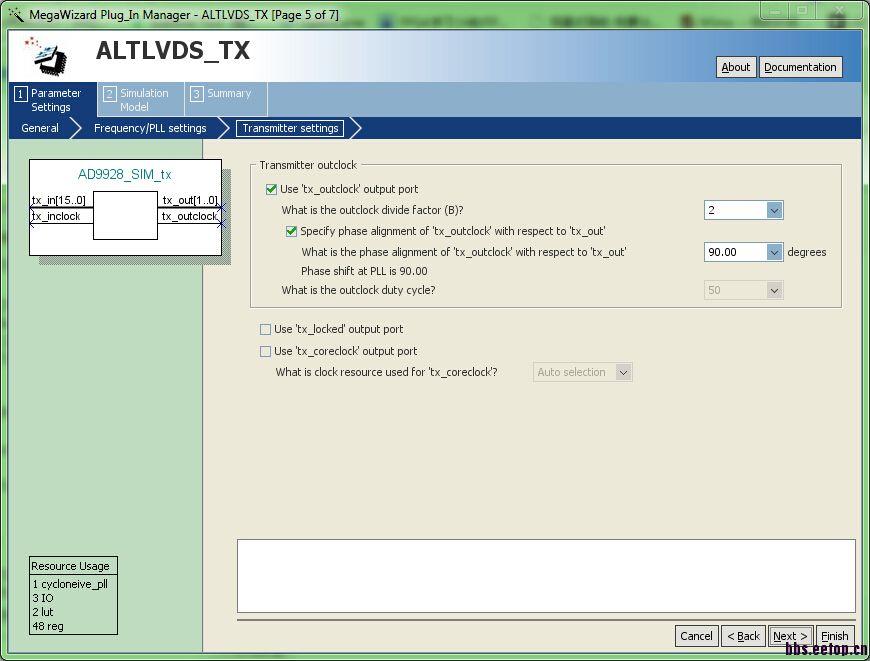

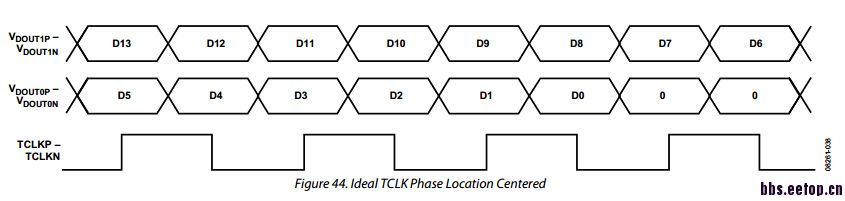

我希望输出的是一个下图这样的波形,所以需要在输出端设置一个90°的相位偏差。但是不论我怎么调整,仿真出来的图时钟无法达到我想要的效果

另外我想请教一下,

1.SERDES开始的24bit数据是用来做LVDS的同步的吗?他是根据什么规律产生的?

2.我如果做一个LVDS_RX的话,这部分同步的数据是否也会被当做正常数据来接收?如何屏蔽掉他呢?

3.LVDS_RX的DPA有什么设置呢?4.我在上图的设置中,输入端并没有改变clk的相位,为什么他的相位和TCLK的相位有偏差呢

5.关于LVDS的同步时序部分,我找不到相关的资料,想请教一下谁有呢?