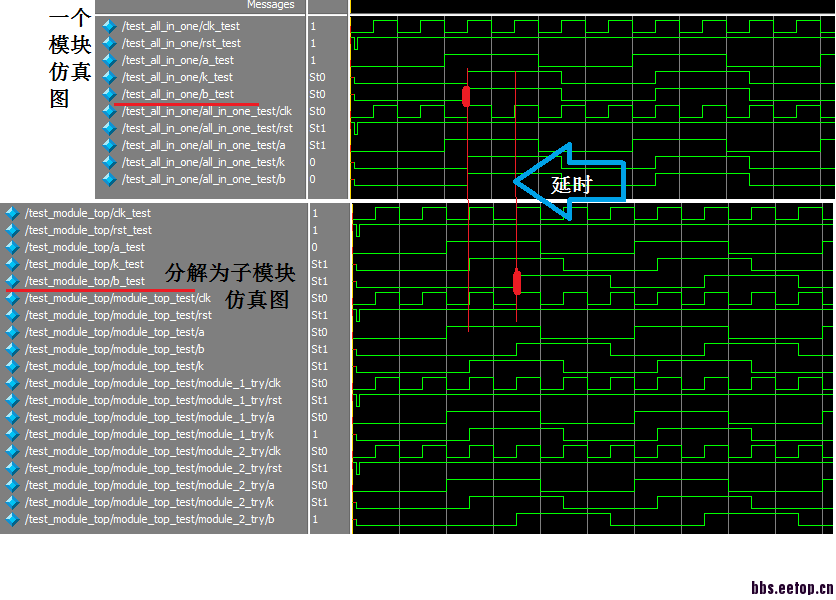

modelsim分模块仿真的延时问题

为什么会产生延迟,怎样才能分模块并取消延迟?

还有,怎样的代码风格是好的呢?我这种写法有什么问题呢?

PS:原代码要复杂一些,需要阻塞赋值。

我把我的代码简化成了下面的样子,仿真效果如图

整体模块的实现:

==============================================

`timescale 1ns/10ps

module all_in_one(clk,rst,a,b,k);

input clk;

input rst;

input a;

output k;

output b;

reg k;

reg b;

always@(posedge clk or negedge rst)

begin

if(!rst)

begin

k=1'b0;

b=1'b0;

end

else

if(a==0)

k=1'b0;

else

k=1'b1;

if(k==0)

b=1'b0;

else

b=1'b1;

end

endmodule

分解为子模块的的代码

===========================================

`timescale 1ns/10ps

module module_1(clk,rst,a,k);

input clk;

input rst;

input a;

output k;

reg k;

always@(posedge clk or negedge rst)

if(!rst)

k=1'b0;

else

if(a==0)

k=1'b0;

else

k=1'b1;

endmodule

————————————————————————————————————

`timescale 1ns/10ps

module module_2(clk,rst,a,k,b);

input clk;

input rst;

input a;

input k;

output b;

reg b;

always@(posedge clk or negedge rst)

if(!rst)

b=1'b0;

else

if(k==1)

b=1'b1;

else

b=1'b0;

endmodule

------------------------------------------------------------------

`timescale 1ns/10ps

module module_top(clk,rst,a,k,b);

input clk;

input rst;

input a;

output b;

output k;

module_1 module_1_try(.clk(clk),.rst(rst),.a(a),.k(k));

module_2 module_2_try(.clk(clk),.rst(rst),.a(a),.k(k),.b(b));

endmodule

求各位大大发表看法 能拓宽一下我的思路也好啊

时序逻辑里面阻塞赋值是不对滴!

唔 完全不可以吗 我有把全代码都改成非阻塞赋值过,然后延迟悲剧的变成了两个时钟周期,感觉还没阻塞的效果好,于是就选用阻塞了 - -! 是我的代码编写思路有问题么?

把module_2中

if(k==1)

改为

if(a==1)

额 可能是我把代码简化后a和k的功能看起来重复了吧,但在具体的代码中,a是10位的,k是1位的,k要根据a的取值来决定,而b的值不仅与k有关也跟其他的参数有关,我只是为了问题的简明把其他的参数去掉了

其实,我问题的关键是,为什么会产生延时?

从你贴出来的代码看,分解后的和未分解的并不等价。

是指在model_2里 if(k==1)

b=1'b1;

else

b=1'b0;

在if(!rst)的嵌套里吗? 我把这一段拿出来了,改成了和all_in_one一样和复位语句并列的样子了,仿真出来后还是有一个时钟周期的延时。

求问大大,还有哪里是我没注意到的吗?

未分解的时候,a决定k的值,这个k又决定b的值。所以我在5楼的改法,是与未分解的等价的。如果这样改后,仿真波形还有差异,我也不知道了。

去掉a和b中间的过渡k后,波形确实一样了。 可是这样就是a决定b了。在应用的时候我想用k控制b,我的写法上是在哪里不等价呢

都是阻塞赋值问题。

未分解的模块中,那个if(a==0)语句赋值的k,是会影响if(k==0)语句执行结果的,所以a决定b是这段代码所表达的逻辑。显然,这不是你的本意。

在第一个没有分解的module里面两个if判断是在一个begin end 块里面的虽然begin end块内是顺序执行的但是是在一个时钟上升沿到来的时候完成的,这样就会出现你仿真的结果,而当你分解玩以后连个if是并行执行的,信号到达管脚的延时不一定是一样的,所有就会造成module1中k已经等于1了而module2没有采到这样只能等到下一个时钟的上升沿才会采到值,就会出现你仿真的情况,不知道我理解对不对

理解了一半吧- -! 感觉自己还是太弱了,刚刚看了个代码风格的帖子,那些不该犯的错误我基本都犯遍了。估计我还要多些点代码才能理解吧。

真的是万分感谢~

好像有点道理

谢谢啦

请高手指教

想知道,模块嵌套调用的时候,用modesim该怎么仿真啊