verilog 仿真和实际看波形不一致(if判断条件不生效)

时间:10-02

整理:3721RD

点击:

代码如下,开发硬件环境为xilink v6 ,软件为ise13.1 。代码非常简单,现在用isim仿真看,波形没有问题。

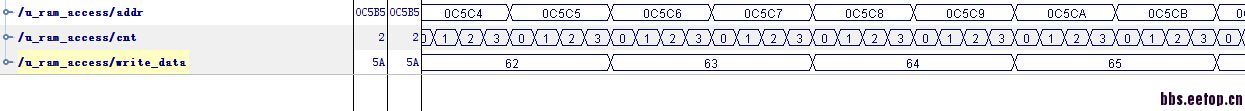

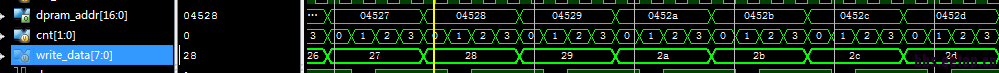

但是用chipscope 抓取波形,发现那个(cnt==2'b11)判断有时侯该成立的时候不成立。

always@(posedge clk_div4 or negedge rst_n)begin

if(!rst_n)

cnt<=2'b0;

else

cnt<=cnt+2'b1;

end

always@(posedge clk_div4 or negedge rst_n)begin

if(!rst_n)

write_data<=8'h0;

else if(addr==17'h1fffe && wr==1'b1)

write_data<=8'h0;

else if(cnt==2'b11)

write_data<=write_data+8'h1;

end

最后一个if else不是完备的,上板会出现问题吧

如果不完备 不是锁存器么 就是write_data 不变化 我的理解是这样的~

你好,非常感谢你的回答

我加了个else write_data<=write_data;

完备了 仍然是有这个问题

else if(addr==17'h1fffe && wr==1'b1)

write_data<=8'h0;

else if(cnt==2'b11)

write_data<=write_data+8'h1;

这两句话会不会同时有效?同时有效会出现什么情况

可能是chipscope信号分配问题,你再检查下wdata信号连接到chipscope的数据和你分配BUS的信号是不是一致的。感觉这里的wdata 的最低位没了。

这现象太普遍了

同时出现的话 按照顺序来看 write_data为0

nice 我太粗心了 ,好像write_data 最低位没有拉过去。你太帅了,这猜测都猜出来了