求助:如何用FPGA来验证AFC(自动频率控制)

时间:10-02

整理:3721RD

点击:

RT~

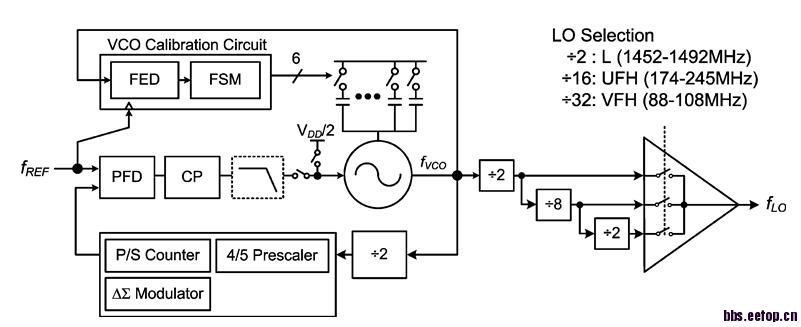

由于AFC里面的fvco很快,所以我采用的办法是先进行一个分频得到一组四相时钟再进行记数的,但是即使这样counter的时钟还是有500M左右,不知道fpga能否跑这么高的频率,而且由于AFC的结构问题,为了得到一个反馈的fvco,用fpga怎么实现啊?因为涉及到锁相环的问题~

AFC的结构如图所示~

求帮助,谢谢~

自顶,求帮助

你这个要求太高了吧

貌似这个要用模拟做啊

看是用哪种FPGA了,如果是高速的,光个计数器,跑500M还是可能的。

对,vco那块是模拟的,可我要用一个数字信号控制电容的开关,这儿又是数字控制模拟,所以我不知道怎么验证~

想问问有什么可行的验证方法~

4分频有500M。2G的信号直接AD到数字域进行处理?

要是你实在没法的话只能用500M时钟来计数的话,我有个法子,

分两步时钟:

cnt1[1:0] ,两位计数器,这样可以跑较高速度,

cnt2[9:0], 多位计数器,if(cnt1 == 2'd3)时加1,同时作多周期约束,相当于降到125M了,

谢谢~

再问问,那vco那部分我怎么加进来一起进行验证呢?

貌似是这样的,给的指标是说counter的时钟信号有500M

小编问一下你这个图的参考文献是哪个?