新手求助,可赋初值4位加法器,写了testbench,好像一直没有运行里面的initial

时间:10-02

整理:3721RD

点击:

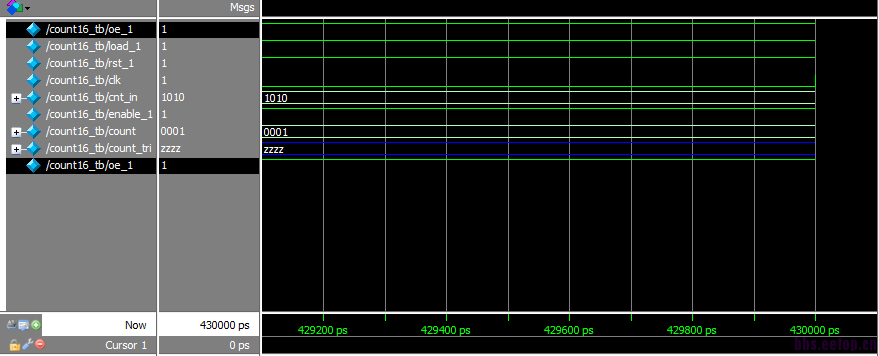

我写了一个test bench来测试一个4-bit 加法器。 加法器里有一个输出使能控制信号,该信号为低时可输出技术,否则输出Z。在test bench里已经对该使能信号做了控制,可是波形里始终是无效的。求大神帮忙啊!感激不尽!

我写了一个test bench来测试一个4-bit 加法器。 加法器里有一个输出使能控制信号,该信号为低时可输出技术,否则输出Z。在test bench里已经对该使能信号做了控制,可是波形里始终是无效的。求大神帮忙啊!感激不尽!testbench代码

- `timescale 1ns / 100ps

- module count16_tb ;

-

- reg oe_1 ;

- reg load_1 ;

- reg rst_1 ;

- reg clk ;

- reg [3:0] cnt_in ;

- reg enable_1 ;

-

- //Outputs from the Device Under Test are wire type

- wire [3:0] count ;

- wire [3:0] count_tri ;

-

-

-

- //Initial blocks are sequenctial and start at time 0

- initial

- begin

- $display($time,"<<Starting the simulation>>");

- clk=1'b0;

- rst_1=1'b0;

- load_1=1'b1;

- enable_1=1'b1;

- cnt_in=4'b0;

- oe_1=1'b0;

- #20 rst_1=1'b1;

- $display($time,"<<Coming out of reset>>");

-

- @(negedge clk);

- //load passed initial value to the counter.

- load_counter(4'hA);

- @(negedge clk);

-

- $display($time,"<<Turning ON the count enable>>");

- enable_1<=1'b0;

-

- wait(count==4'b0001);

- $display($time,"<<count=%d-Turning OFF the count enable>>",count);

- enable_1=1'b1;

- #40;

- $display($time,"<<Turning OFF the OE>>");

- oe_1=1'b1;

-

- #20;

- $display($time,"<<Simulation Complete>>");

- $stop;

-

-

- end

-

-

-

-

-

- //Instantiate the Device Under Test

- count16

- DUT (

- .oe_1 (oe_1 ) ,

- .load_1 (load_1 ) ,

- .rst_1 (rst_1 ) ,

- .count (count ) ,

- .clk (clk ) ,

- .cnt_in (cnt_in ) ,

- .enable_1 (enable_1 ) ,

- .count_tri (count_tri ) );

- //Create a 50Mhz clock.

- always

- #10 clk=~clk;

-

-

-

- //The load_count task loads the counter with the value passed.

- task load_counter;

- input [3:0] load_value;

- begin

- @(negedge clk);

- load_1<=1'b0;

- cnt_in=load_value;

- @(negedge clk);

- load_1=1'b1;

- end

- endtask

- endmodule

下面是计数器的代码

- `timescale 1ns/100ps

- module count16(count,count_tri,clk,rst_1,load_1,enable_1,cnt_in,oe_1);

- output [3:0] count;

- output [3:0]count_tri;//tri_state buffers

- input clk;

- input rst_1;

- input load_1;

- input enable_1;

- input [3:0] cnt_in;

- input oe_1;

- reg [3:0] count;

- assign count_tri=(!oe_1) ? count : 4'bZZZZ;

- always @ (posedge clk or negedge rst_1)

- begin

- if(!rst_1)

- begin

- count<=#1 4'b0000;

- end

- else if(!load_1) begin count<=#1 4'b1010;

- end

- else if(!enable_1) //enable_1 is the enable signal of counting.

- begin

- count<=#1 count+1;

- end

- end

- endmodule

-

-

为什么单步调试就可以正常,直接run all就不行呢?

波形的最小精度可以放大些,现在才1000ps,也就半个clk,怎么看

clk都没显现出来

也可以看看printf信息

确定你testbench中的 $stop这个函数的时间位置是正确的嘛,在我用VCS仿真的时候,执行./simv时,vcs告诉我仿真停止在 $stop这一行,你可以查一下你的仿真时间的长度是否够。我是注释掉 $stop这个函数仿真可以看到波形,没有问题。

先把 oe_1 = 1 注释掉,再看看

是不是仿真时间太短。clk才刚到第一个上升沿

确实是波形精度的问题,其实已经正常仿真了,只是我的时间范围没有调好,谢谢你!也谢谢各位高手的回答。

不错