关于在使用chipscope中遇到的问题求解

刚开始使用chipscope, 有很多地方还不是特别明白,忘各位前辈不吝赐教

(1)我的设计大致思路如下:

两块FPGA通过导线连接,进行通信

FPGA1 FPGA2

clk_out ------> clk_in

data_out[1:0] ------> data_in[1:0]

en_out ------> en_in

clk_in <------ clk_out

data_in[1:0] <------ data_out[1:0]

en_in <------ en_out

(2) 通过chipscope分别取抓取两块板子上的信号,发现:所有的output均正确,但是input信号会有不太期望的信号出现,具体如下:

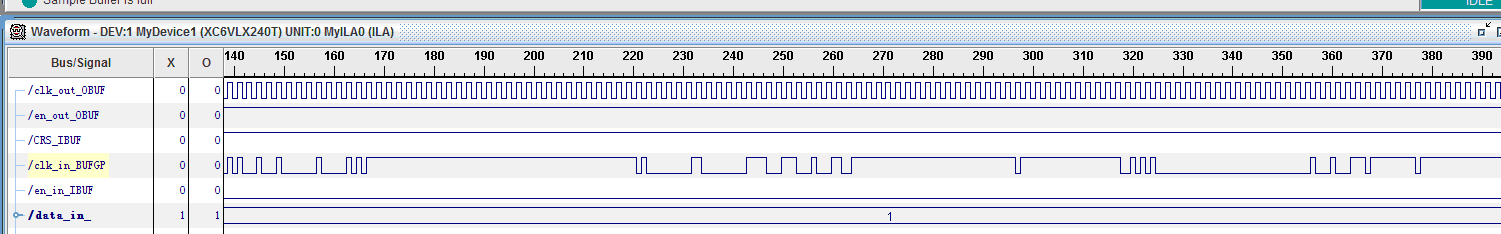

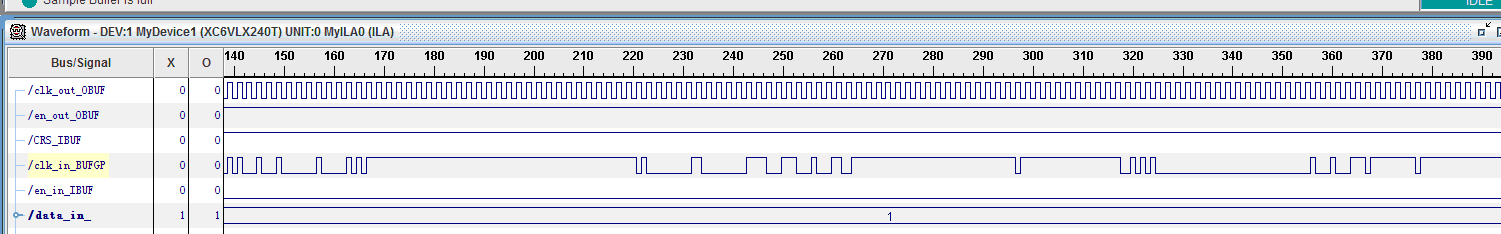

a. 用100M的时钟去抓取50M的clk_in, 出现以下现象:

(clk_in有一段时间的高电平,或者低电平)

问题:在确定clk_out正确的前提下,clk_in为何会产生这样的现象呢?是因为clk_in是时钟,所以会在传输过程中产生错误吗?还是跟我的时钟频率有关系。

b. (感觉自己的截图有问题)

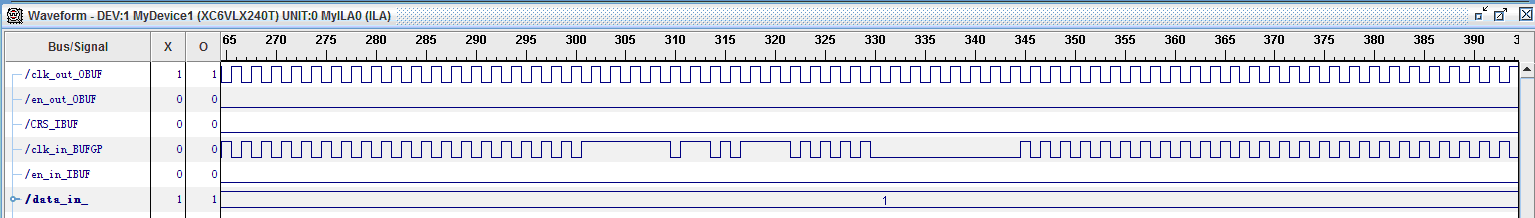

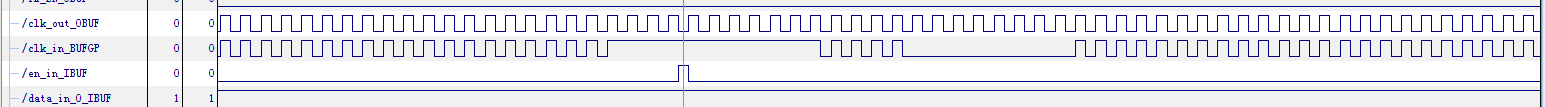

用100M去采样en_in信号时,会出现短小的脉冲高电平(理想情况下是不会产生的,en_in有效时一定是较长的一段高电平)

关于这个问题的深入实验表明:(以采样FPGA2上的信号来举例)

当拔掉FPGA2上连接clk_in的线,en_in就机会不会产生这样的短脉冲信号;

当拔掉FPGA2上连接的clk_out的线,en_in还是会产生这样的脉冲信号;

进一步确认:在FPGA2中把clk_in和clk_out引脚挑换,en_in的短脉冲还是只和clk_in信号有关

问题:对于上述现象的产生原因我没有想通。

c. 【补充】我现在的数据会出错,主要原因在于en_in会产生小脉冲(本不应该产生),尤其是在en_out有效期间,en_in产生小脉冲的情况特别严重(chipscope波形看起来类似于是时钟),我尝试用两级D触发器来过滤这个毛刺,但是效果不好,我想是因为毛刺过于多的原因。

这种脉冲会让我检测到错误的en_in上升沿,响应的数据处理就会有错。我认为主要在于两块板子的连线上,数据会产生干扰,不知道能否有什么办法可以减少这种情况。

clk_in不稳定

clk_in不稳定

en_in出现短脉冲

时钟采出来好像就这个样子

(1) 100M采样50M的时钟就会出现这种情况吗?我不是很理解,能详细说明一下吗? 100M和50M的时钟是两个晶振通过DCM产生的,即使频率有误差,占空比应该不会有误差吧,

而且根据clk_in对数据进行处理时,觉得有部分clk_in没有真确输入,导致处理时会有问题。

(2) en_in出现脉冲信号又是什么情况呢?

我经验太少,很多不太明白的地方,望指教哈。我也有把时钟信号拿出来采,就是这个样子。不是说时钟不正常,我整个工程运行也很正常。为什么这样,我也说不好,要不你试试不用两倍的关系看看

虽然还不是很明白,但是谢谢你啦。我再多做做实验看看。

实验完了,把结果说说,让大家看看呗You sample clock with chioscope of two fpga board are same clock source.

If not that may be will sample the wrong point.

两块FPGA,用chipscope时只能分别对某一块板子抓取信号,此时抓取信号的时钟是由该块板子中的晶振DCM生成的100M时钟,那么两块FPGA的时钟源必然来自两块板子的晶振,肯定会不一样啊。 以上是我的理解,不知道是否有不对的地方,望指教。

补充:我现在的数据会出错,主要原因在于en_in会产生小脉冲(本不应该产生),尤其是在en_out有效期间,en_in产生小脉冲的情况特别严重,我尝试用两级D触发器的过滤这个毛刺,但是效果不好。但是这种脉冲会让我检测到错误的en_in上升沿,响应的数据处理就会有错。不知道能否有什么办法减少这种情况。

From your note I thought the output signals of the FPGA1 doesn't latch by the flip-flop with the clk_out.So your input signals of the FPGA2 had glitch.

1. You d-Flip-Flop should add on the FPGA1 output side.

3. Does the clock of the FPGA2 on phase with the clk_in? If not you can do item 3.

2. You may be tuning the clock phase with DCM of the FPGA2 can on phase the clk_in.

最近忙完了,回来把帖子更新一下。 问题已经解决,关于clk的采样结果主要是因为chipscope中的采样时钟和被采样信号不同源造成的,所以采样到的信号看起来会觉得有问题。

第二,就是产生glitch的原因主要是因为两块板子没有共地,且连接两块板子的PIN脚电压没有匹配,一边是2.5V一边是3.3V,匹配后就不会有这样的问题了。

学习了