新人求助,关于Quartus中RAM的几个问题。

时间:10-02

整理:3721RD

点击:

版本Quartus 11.0SP1 64bit新人,接触不久,还在学习中,现在做一个简单的将波形数据写入RAM中,再将RAM中数据读出,(给DAC产生波形的,这部分师兄做的,我直接拿来用的)。

现在遇到了两个问题,望各位帮个忙,不胜感激。

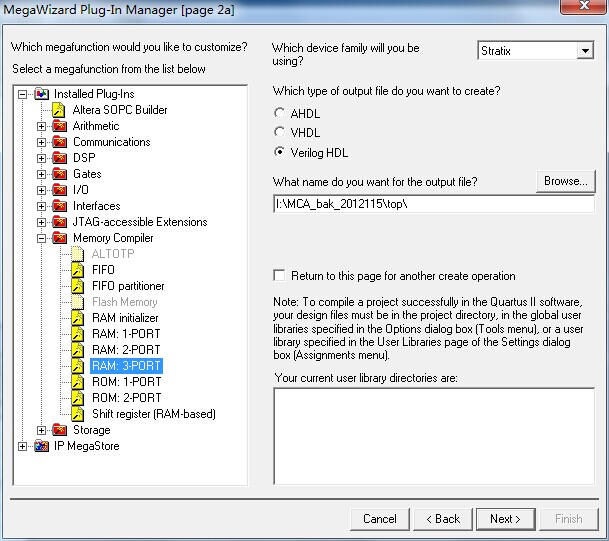

1.这里只有RAM:2-PORT的,首先遇到的问题就是这块RAM和我所想要的不是同一个效果。

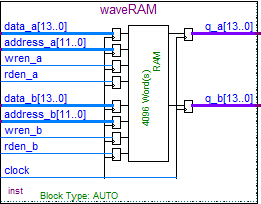

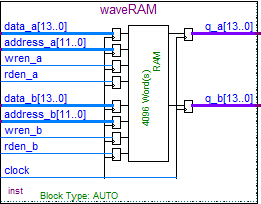

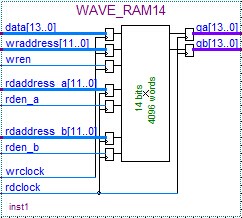

我想要的是写一根地址线和数据线。将数据写入之后,再通过另外两根读地址线将数据读出,因为那个DAC的输入是两个输入,分别是一组数据中的奇偶两组数据。这个RAM如图所示,两个数据线两个写读共用的地址线,跟我想要的不一样,它这个感觉就像是两块RAM一样,各干各的。这个我只能在RAM前面加一个自己写的将数据分开的程序,麻烦是一点,主要是设计的频率降低了。

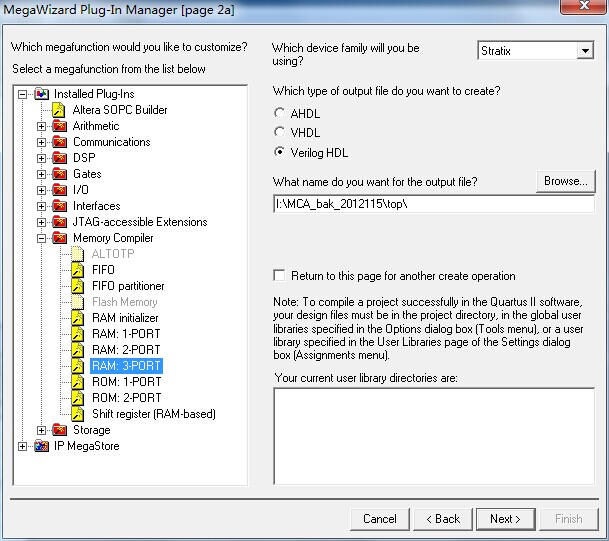

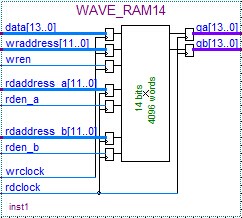

而我无意在Quartus 9.1中找到了一个RAM:3-PORT的,完美的达到了我想要的东西。

这个,我想能不能不换版本,解决我遇到的这个问题?。

2.RAM的问题,现在程序运行正常,使能我还没控制都拉高的,就是一直写一直读。波形能够输出我想要的,但是我一加使能就不对了。

我想的是RAM中写完波形数据后,WREN拉低。读是一直读的,但是写完一遍,然后让WREN一拉低之后,输出一直就为0了,好像RAM中没有数据了一样。不知道是不是我对RAM的理解有问题?我想只要每个地址写入一个数之后,这个RAM中写过一次之后,数据应该就存在了RAM中,不会变的吧?

现在遇到了两个问题,望各位帮个忙,不胜感激。

1.这里只有RAM:2-PORT的,首先遇到的问题就是这块RAM和我所想要的不是同一个效果。

我想要的是写一根地址线和数据线。将数据写入之后,再通过另外两根读地址线将数据读出,因为那个DAC的输入是两个输入,分别是一组数据中的奇偶两组数据。这个RAM如图所示,两个数据线两个写读共用的地址线,跟我想要的不一样,它这个感觉就像是两块RAM一样,各干各的。这个我只能在RAM前面加一个自己写的将数据分开的程序,麻烦是一点,主要是设计的频率降低了。

而我无意在Quartus 9.1中找到了一个RAM:3-PORT的,完美的达到了我想要的东西。

这个,我想能不能不换版本,解决我遇到的这个问题?。

2.RAM的问题,现在程序运行正常,使能我还没控制都拉高的,就是一直写一直读。波形能够输出我想要的,但是我一加使能就不对了。

我想的是RAM中写完波形数据后,WREN拉低。读是一直读的,但是写完一遍,然后让WREN一拉低之后,输出一直就为0了,好像RAM中没有数据了一样。不知道是不是我对RAM的理解有问题?我想只要每个地址写入一个数之后,这个RAM中写过一次之后,数据应该就存在了RAM中,不会变的吧?

问题1:小编你需要的是一个三端口的RAM,而三端口的RAM在QII 9.1之后就被ALTERA公司干掉了,所以你的QII 11.0里面肯定没有这个3-PROT的RAM了,至于解决这个问题有两个办法:办法一,你将同样的数据写到两个RAM里面,两个RAM读地址不一样就可以了。办法二,你用QII 9.1例化一个3-Port的RAM ,然后copy到QII 11.0工程中使用,这样就可以不更换版本了。

至于问题二,我没太看明白小编的意思,所以你可以再描述详细点,后面就会有人给你答案了

路过,门外看看

不是特别理解LZ的意思。但我觉得LZ只需要一个SDP RAM即可。也就是一个读地址一个写地址,一个数据输入,一个数据输出和一些控制信号的RAM即可。

你的DAC两个输入数据的地址不是一样的吗?

2:肯定是你的逻辑错了!不是RAM的问题!

另外一个建议就是既然你不大了解RAM,直接用RTL写一个,让Quartus综合,你就不用去管细节了。

小编想发的是非连续信号,这个单个双口RAM是可以实现的,控制的话是肯定没问题的。不写的时候可以控制使能,也可以控制写地址。不行的话,就是你的程序的问题,另外,根据你的想法,如果数据量不是很大的话,那用ROM也是满足要求的。

楼上是正解!工作在双端口一写一读模式下,读端口的使能信号是控制读使能的