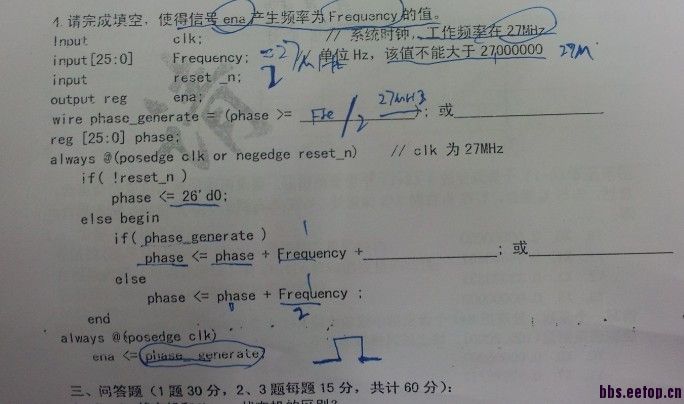

找工作遇到的FPGA逻辑的笔试题目,欢迎大家来讨论

第一题我来答一下

ena<=phase_generate可知,phase_generate=ena, 也等于Frequency。

从 phase<=phase+Frequency可知, 每个时钟,累加一个Frequency.

所以累加速度为 Frequency*n, n为时钟周期数。而phase的值也为Frequency*n

假设Frequency为1,那么,(phase>= ) 变高的条件既为, (n>=27M/2), 也就是1/2秒既为高,如果Frequency 不为1,那么就要乘上Frequency, 即为,n*Frequency>=27M/2, 而phase的值也为Frequency*n, 所以第一空为27M/2=13.5M。

第二空为

记数器最大记数为2^26, 而实际最大为27M,所以多出40108864,而多出的必须填满,所以 空为

40108864/(13.5M/Frequency)=2.971*Frequency不是应该填(27M-1)么?最终产生的ena只有一个clk的高电平,然后phase有个跳变,会在下一个周期变成低电平。

顶一下,我也遇到这题了

第一道题还是挺巧妙的,一开始我看到这个题目认为肯定会用到除法器,而且还有精度问题,结果看下面的代码我发现他直接用freq.循环累加的方式实现了这个功能,绕过了除法器,学习了!

他为什么不直接写成:

if(phase_gen)

phase <= 26'h0;

else

phase <= phase + Freq.这样得到的输出频率就不是Freq了

我认为你的解法没错,实际得到的输出占空比为50%。

补充一下我的看法:

1)如果27M和Freq非倍数关系,那么得到的输出信号的不具备规则频率,不知道这个输出是否还有意义;

2)系数2.971仅在数学原理上成立,在代码中不具有实际意义。

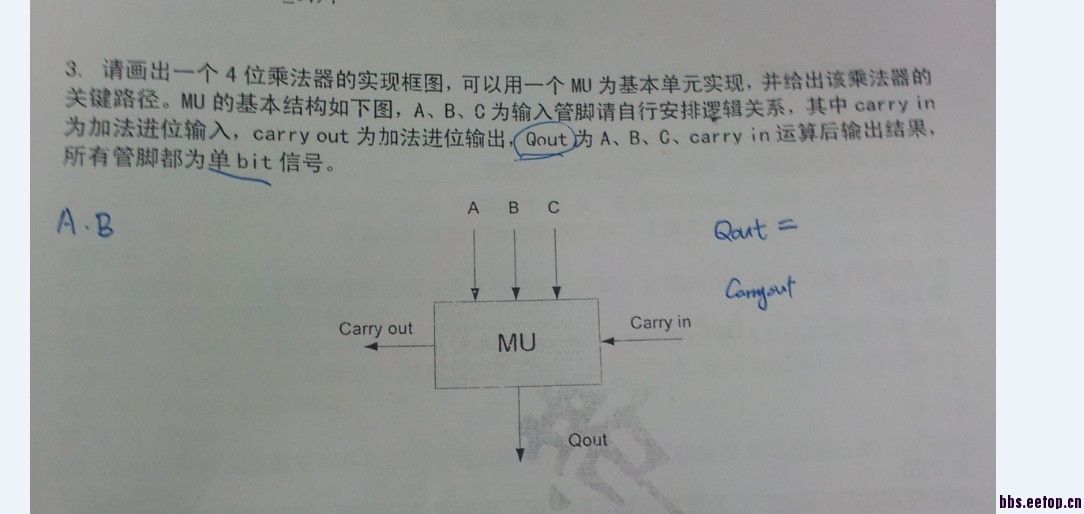

第二题,最容易想到的办法就是把MU当成全加器,不过浪费掉了一个输入引脚;可以在此基础上考虑一下优化的办法,比如把MU设计成压缩单元之类的。弱弱的问一下你们有要看新机会的吗,可以加我QQ:2509695849

搞不太懂,按你这种说法,我想产生一个25m的,那么输出的信号实际上是等duty的2分频,而如果27m/freq为整数,则按整数处理了,即如果是1点多,则按2处理,这样的结果岂不是不符合要求。

果断不对啊,2楼正解mark下,有空在看

有趣的考題, 感謝分享

小数点乘以数量级就不一定是小数了,至少可以很接近或等于理论值第一道题看了半天没明天它要说的是什么意思。

惭愧,,学习好高深呀,