FDCE触发器的CE端亚稳态的问题

时间:10-02

整理:3721RD

点击:

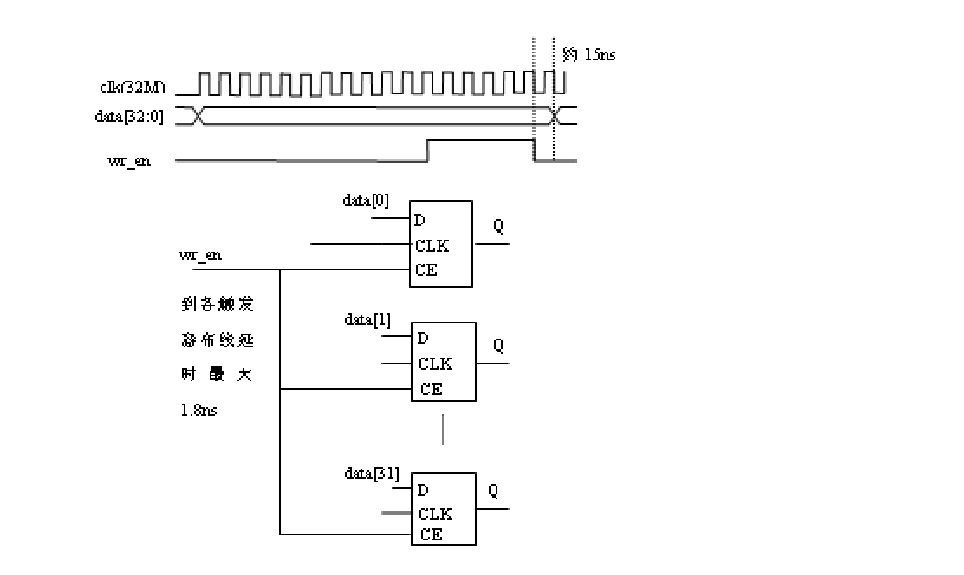

在FPGA的FDCE触发器中,若D端数据一直处于稳定状态,CE端接了一个异步逻辑。那么,若时钟沿到来时CE端处于亚稳态,Q端输出应该怎么分析?会不会输出一个不确定的值?

求大神帮解。

图有点看不清,右上角那个时间是15ns。

其中,wr_en是由组合逻辑产生的异步信号,像这种情况会不会引起reg寄存器的写入错误?

相关语句:

always @(posedge clk or negedge rst_n)begin

if(!rst_n) reg<=32‘d0;

else if(wr_en) reg <=data[31:0];

end

从时序图上来看,WR_EN这个要持续好几个clk cycle,个人意见可以换一种做法,来尽量避免异步设计。用clk来采样wr_en,把这个信号当作一个data来sample,

- reg wr_en_f1;reg wr_en_f2;

- reg wr_en_f3;

- always @(posedge clk or negedge rst_n) begin

- if(!rst_n) begin

- ...

- end

- else begin

- wr_en_f1 <= wr_en;

- wr_en_f2 <= wr_en_f1;

- wr_en_f3 <= wr_en_f2;

- end

- wire wr_en_f3_pos = wr_en_f2 && wr_en_f3;

然后用wr_en_f3_pos来触发data的sample。

ff的输入端,包括D CE SR,如果不是与CLK同步的,都会产生问题。

多数情况下,有可能不会出现问题,但是问题一定是存在的,只是发生的概率问题。

我们之前做过的设计,SR端用了异步信号,产生了奇怪的上电错图问题,这个是很难debug的,因为复现频率太低。

同意LS两位。

只要是异步信号就必然存在亚稳态,只是概率的高低问题。典型的异步信号从慢速时钟域进入高速时钟域的处理。2楼是正解。但是wr_en_f3_pos应该是取wr上升沿,应该是2楼笔误。

用写使能打2拍之后,判断其上升沿,然后写入,在该上升沿脉冲期间写使能和数据均稳定。如楼上几位所说。

为什么这个写使能这么宽,数据跟这个clk也不是同步的吧