一个具体问题:组合逻辑在CPLD中的现象(急!)

时间:10-02

整理:3721RD

点击:

请教大家一个实际问题:

DS[1:0]是CPLD的两个输入信号,经过如下代码锁存:

always @(posedge Clk or negedge nReset)

begin

if (!nReset) begin

DSXout <= 1'b1;

NDSX <= 1'b1;

end

else begin

NDSX <= & DS;

DSXout <= NDSX;

end

end

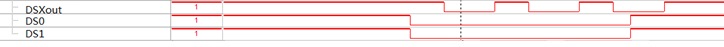

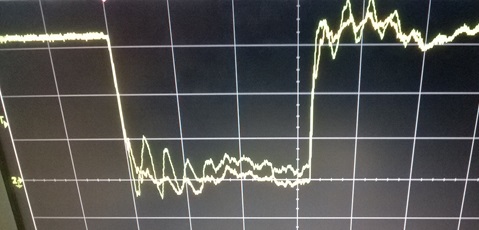

为何会在导入FPGA后的signaltap上看到如图1所示的情况?按照我的理解,虽然&DS作为组合逻辑可能有不稳定的地方,但也应该是竞争冒险那种情况、高低电平切换的边缘出问题?因为我在CPLD信号输入的源端用示波器点了,输入并没有毛刺(如图2,探头接地粗糙所以过冲大),那么该如何分析问题的来源,是逻辑写法问题还是CPLD管脚接触不良呢...求赐教!

DS[1:0]是CPLD的两个输入信号,经过如下代码锁存:

always @(posedge Clk or negedge nReset)

begin

if (!nReset) begin

DSXout <= 1'b1;

NDSX <= 1'b1;

end

else begin

NDSX <= & DS;

DSXout <= NDSX;

end

end

为何会在导入FPGA后的signaltap上看到如图1所示的情况?按照我的理解,虽然&DS作为组合逻辑可能有不稳定的地方,但也应该是竞争冒险那种情况、高低电平切换的边缘出问题?因为我在CPLD信号输入的源端用示波器点了,输入并没有毛刺(如图2,探头接地粗糙所以过冲大),那么该如何分析问题的来源,是逻辑写法问题还是CPLD管脚接触不良呢...求赐教!

下面两个相与得到上面的

示波器点的DS0和DS1波形

看错了,请无视本楼.....

能再看看你的reset信号吗?如果复位没问题,那你就得对ds信号做处理了

楼上正解,

你可以尝试一下,逻辑不用复位看看!

量一下复位信号的电压~