关于CDC的同步器问题!

时间:10-02

整理:3721RD

点击:

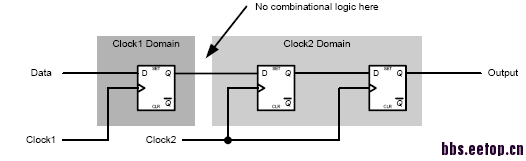

在看最简单的打两拍的同步器(如图)时看到这样一句话:The signal crossing clock domains stays high and low for more than a two clock cycles in the new clock domain.A requirement of this circuit is that the signal needs to transition to its invalid state before it can become valid again.1:为什么需要保持两个时钟啊?表示不理解!

2:什么叫做invalid state?

同步器

当需要考察数字电路在不稳定状态下(setup/hold不满足、电压不足...)如何工作时,就要用模拟电路的思路来分析。

这个同步器之前没有注意这两个条件,呵呵!

肿么又是你,肿么又是这句话。

1.同步器并不能保证信号跨时钟域failure的几率为0,只是尽可能降低出错概率,这里涉及到MTBF(Mean Time Between Failure)的计算,一般讲跨时钟域的文档都会提到。至于为什么是2个,我觉得是一个经验参数,一般来说,2个DFF的Synchronizer已经可以把出错几率(1/MTBF)降到很低(此结论有待考证),对一般系统足够了。

2.不知道。

谢谢,我自己再多看看其他资料,看看怎么说

觉得原因是亚稳态的resolution time和MTBF~

保持两个周期是因为要确保信号能被接收端采到

楼上正解

學習了

"保持兩個週期是因為要確保信號能被接收端採到"

好东西,学习