dc各种时序计算问题

时间:10-02

整理:3721RD

点击:

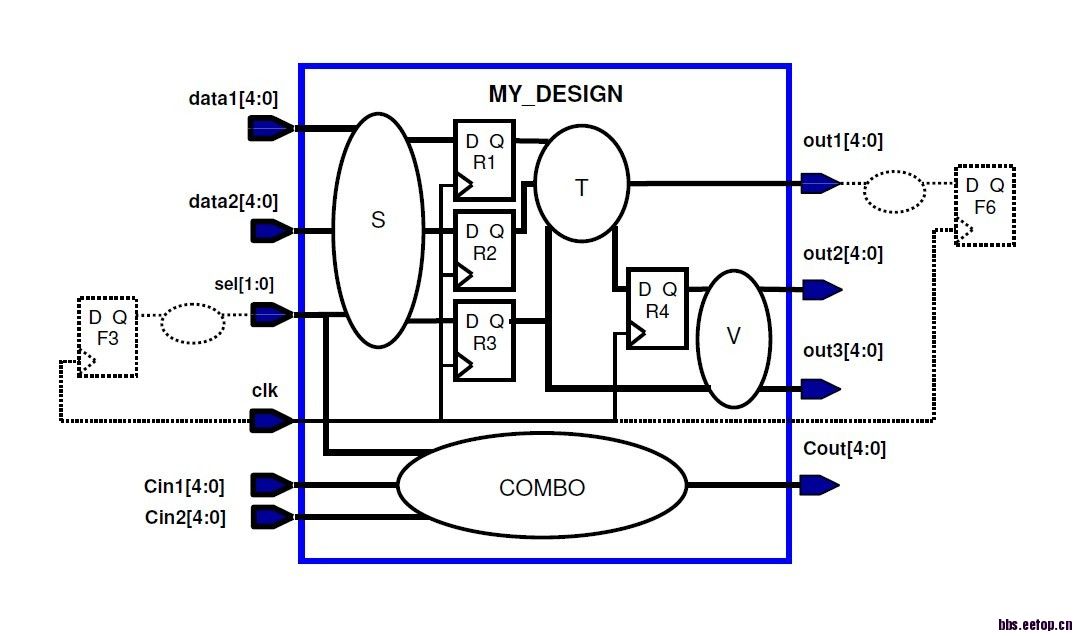

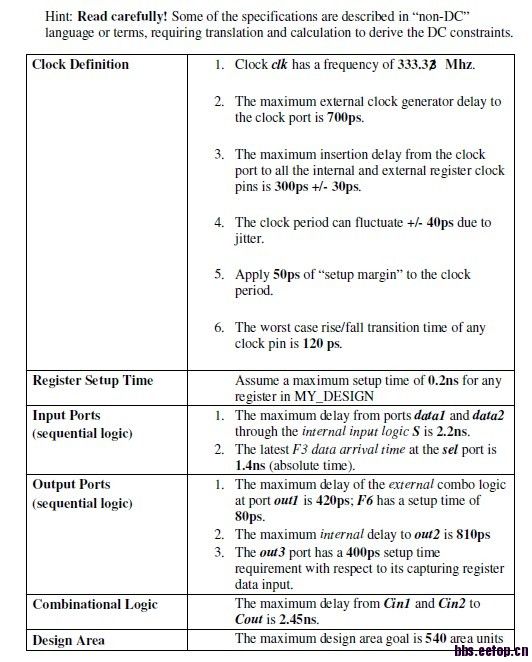

请教下:根据时序描述中的说明,怎么得到下面的TCL约束文件(不清楚红色部分怎么得来的),麻烦各位大牛指点下,谢谢。

create_clock -period 3 [get_ports clk]

set_clock_latency -source -max 0.7 [get_clocks clk]

set_clock_latency -max 0.3 [get_clocks clk]

set_clock_uncertainty -setup 0.15 [get_clocks clk]

set_clock_transition 0.12 [get_clocks clk]

set_input_delay -max 0.45 -clock clk [get_ports data*]

set_input_delay -max 0.4 -clock clk [get_ports sel]

set_output_delay -max 0.5 -clock clk [get_ports out1]

set_output_delay -max 2.04 -clock clk [get_ports out2]

set_output_delay -max 0.4 -clock clk [get_ports out3]

set_input_delay -max 0.3 -clock clk [get_ports Cin*]

set_output_delay -max 0.1 -clock clk [get_ports Cout]

时序的问题不怎么懂,麻烦各位尽量讲得仔细点,谢谢啊。

同求解答。红色部分的那些数字究竟是怎么计算出来的。

set_clock_uncertainty -setup 0.15 [get_clocks clk]

0.3×2 + 0.4(jitter) + 0.5(margin)

inputdelay outputdelay自己看文档的定义吧

set_input_delay -max 0.3 -clock clk [get_ports Cin*]

set_output_delay -max 0.1 -clock clk [get_ports Cout]

只要保证两者的和为0.4即可(3-2.45(delay) - 0.15(uncertainty ))

您好,我看您发了一个帖子:

”synopsys库文件功耗自己手算问题“

您后来是怎么算的,我最近也想自己算,很急,方便联系我吗?请教下

qq:251269939

clock uncertainty is dominate by the design spec. That is the clock source duty cycle distortion.

input and output delay is dominate by the previous block and next block input/output budget.