设计spi从接口电路,每次读操作(支持单次和burst)都会多读一次,求帮忙!

时间:10-02

整理:3721RD

点击:

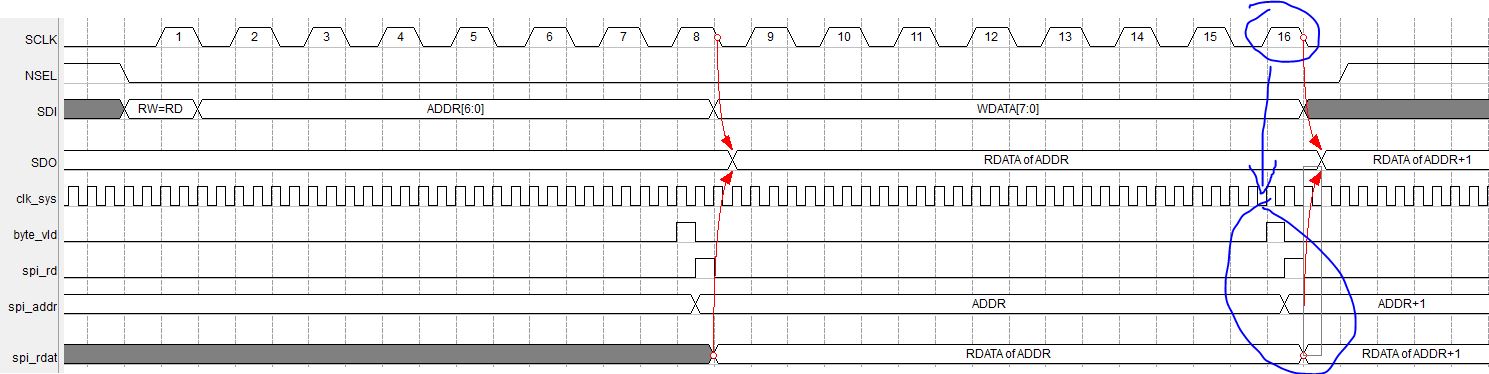

设计一个spi从接口,上升沿采样,下降沿输出,用内部高倍时钟clk_sys过采样设计电路。

如图所示,是一次读操作,第一字节为控制字节,高bit为读写指示,低bit为地址,第二字节为读数据。

在每个字节的最后一个比特产生字节有效信号byte_vld,然后在此基础上再产生读信号,下一拍输出读数据。

由于要支持burst操作,读地址会自动加一。

一次读操作,spi发送N个字节(N>=2)的nsel长度,

结果如图蓝色圈圈所示,一次读操作本该指产生N-1此读操作,现在产生了N次读操作,如果多余的读操作对象时读清寄存器,可能会产生问题。

有没有大侠知道怎么把这最后多出来的读操作干掉,或者有其他方案供参考,先谢谢了!

早点把nsel信号拉起来不就可以了么

读信号在上升沿产生,读数据要在下降沿输出,难道不要最后一bit的读数据!