求大神帮忙解决cycloneiii中写sdc遇到的问题!

时间:10-02

整理:3721RD

点击:

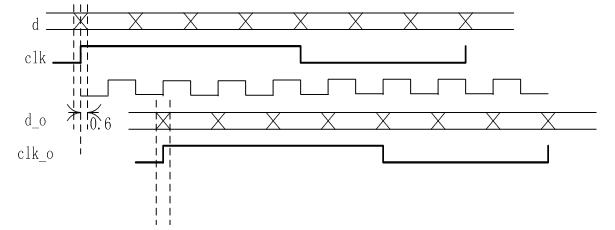

输入d和时钟clk,输出的clk_o和d_o。clk50Mhz,4/7占空比,d为350Mhz,d变化沿相对clk有-0.6ns到

0.6ns的不确定性,要求的输出的clk_o和d_o仍然保持相位相当:具体是允许d_o相对clk_o具有-0.6ns到

0.6ns的偏差。

我现在的做法是:clk过pll生成clk_g(7倍频,180度相移)和clk_d1(同频,0相移)时钟,用clk_g对

clk_d1和d打两拍输出生成clk_o和d_o。约束d相对clk_g有-0.6到0.6的input delay,请问output delay怎么

约束?我现在约束clk_o和d_o相对clk_g的output delay为0.3到2.557(2.857 - 0.3),slack是很大的。请问

大神我应该怎么处理?

或者我的结构就不行,那应该如何做结构?注意我的输出数据是350Mhz的,7倍于时钟。

另外,altrx或者alttx调用暂时不考虑。

0.6ns的不确定性,要求的输出的clk_o和d_o仍然保持相位相当:具体是允许d_o相对clk_o具有-0.6ns到

0.6ns的偏差。

我现在的做法是:clk过pll生成clk_g(7倍频,180度相移)和clk_d1(同频,0相移)时钟,用clk_g对

clk_d1和d打两拍输出生成clk_o和d_o。约束d相对clk_g有-0.6到0.6的input delay,请问output delay怎么

约束?我现在约束clk_o和d_o相对clk_g的output delay为0.3到2.557(2.857 - 0.3),slack是很大的。请问

大神我应该怎么处理?

或者我的结构就不行,那应该如何做结构?注意我的输出数据是350Mhz的,7倍于时钟。

另外,altrx或者alttx调用暂时不考虑。

在线等回复呢

试试 -min -0.8285 -max 2.0285