altera dcfifo使用诡异现象

时间:10-02

整理:3721RD

点击:

贴图:

说明:

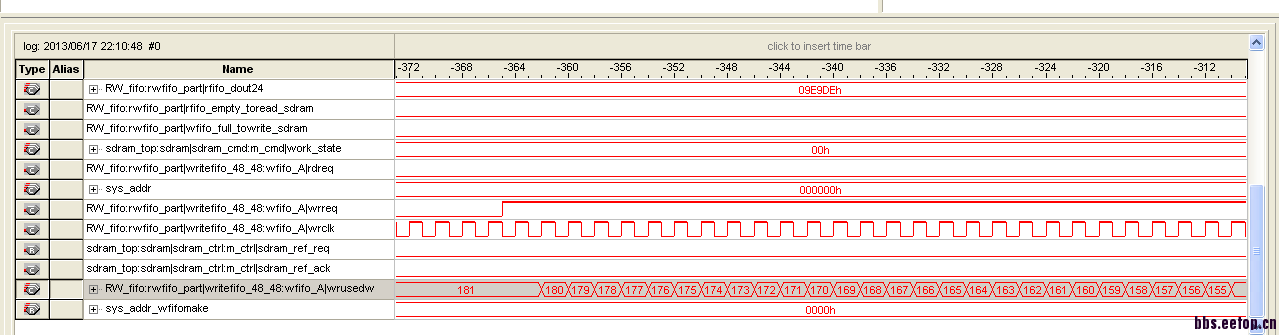

48bit showahead fifo

输入时钟50M 输出时钟100M

同一个pll由25M倍频生成。

目的:fpga模拟外来数据50M 48bit,写入sdram控制器。

诡异之处:wrusedw会越写越小?rdreq确认是低 。

请教高手赐教.

溢出?定制的时候把overflow选项勾掉。

求助继续求助

请高手指点

大家使用都正常吗?没明白小编的意思,wrusedw不就是与写数据量有关么?你写一个数据进去,又不读一个出去的话,wrusedw肯定就-1了,不是这样的么?

tangkuan660

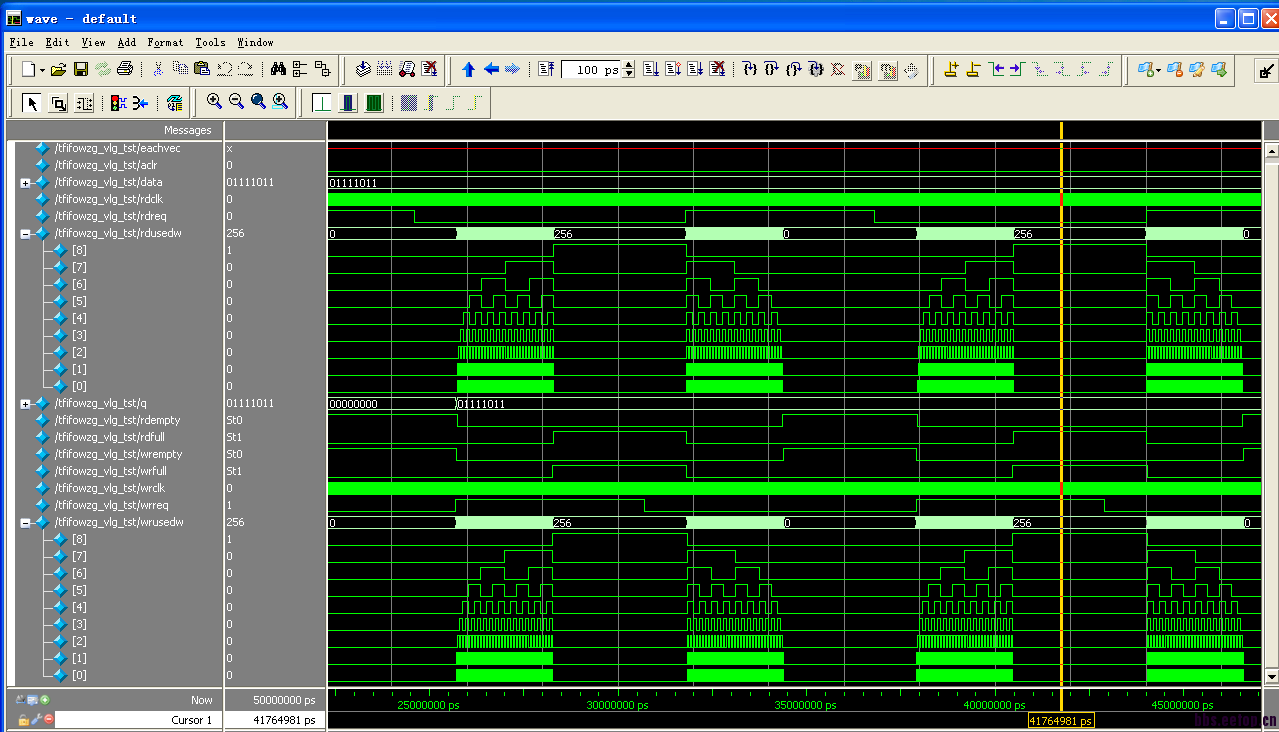

似乎你理解错了。你可以看看仿真的结果。wrusedw是写入数据的个数标志。写入数据这个数增加,读取数据会减小。并且和写入时钟关联,在读取数据到该数据减少一半延迟2-3个读时钟。

希望高手继续指导!大家没有遇到这个问题吗

问题后来去掉sigtapii就好了。怀疑sii抓图问题